ICS2402

Description

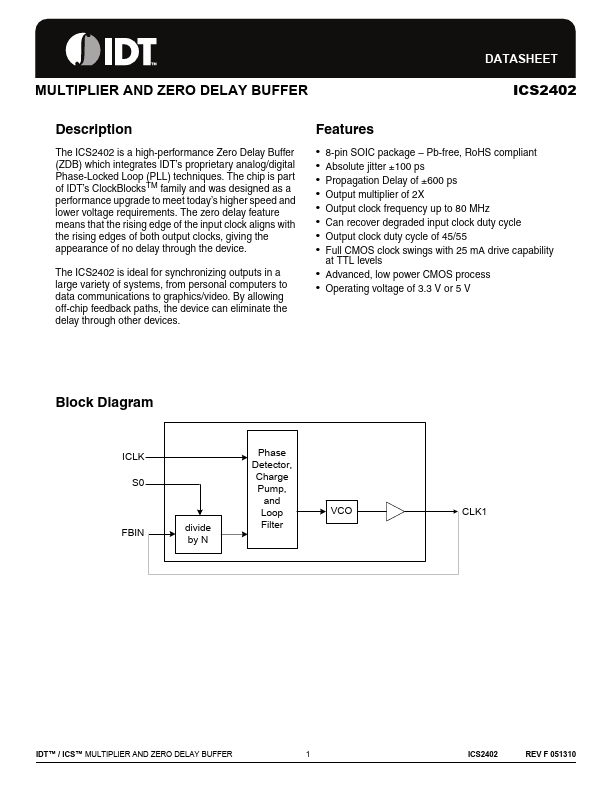

The ICS2402 is a high-performance Zero Delay Buffer (ZDB) which integrates IDT’s proprietary analog/digital Phase-Locked Loop (PLL) techniques. The chip is part of IDT’s Clock Blocks TM family and was designed as a performance upgrade to meet today’s higher speed and lower voltage requirements. The zero delay feature means that the rising edge of the input clock aligns with the rising edges of both output clocks, giving the appearance of no delay through the device.

The ICS2402 is ideal for synchronizing outputs in a large variety of systems, from personal puters to data munications to graphics/video. By allowing off-chip feedback paths, the device can eliminate the delay through other devices.

Features

- 8-pin SOIC package

- Pb-free, Ro HS pliant

- Absolute jitter ±100 ps

- Propagation Delay of ±600 ps

- Output multiplier of 2X

- Output clock frequency up to 80 MHz

- Can recover degraded...