ICS670-03 Overview

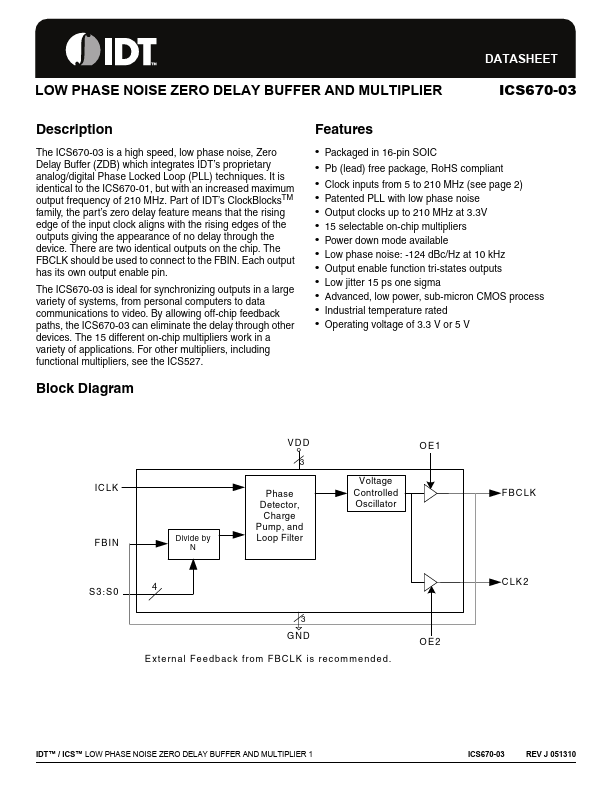

The ICS670-03 is a high speed, low phase noise, Zero Delay Buffer (ZDB) which integrates IDT’s proprietary analog/digital Phase Locked Loop (PLL) techniques. It is identical to the ICS670-01, but with an increased maximum output frequency of 210 MHz. Part of IDT’s ClockBlocksTM family, the part’s zero delay.

ICS670-03 Key Features

- Packaged in 16-pin SOIC

- Pb (lead) free package, RoHS pliant

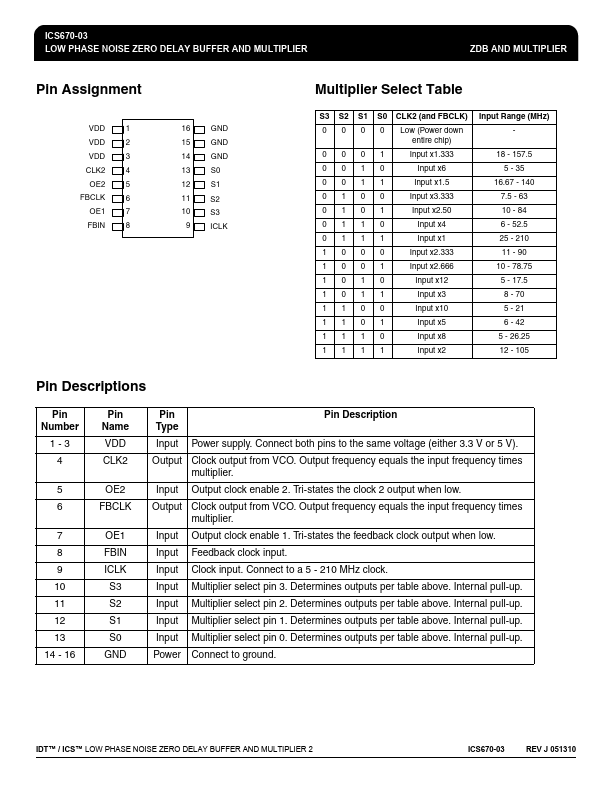

- Clock inputs from 5 to 210 MHz (see page 2)

- Patented PLL with low phase noise

- Output clocks up to 210 MHz at 3.3V

- 15 selectable on-chip multipliers

- Power down mode available

- Low phase noise: -124 dBc/Hz at 10 kHz

- Output enable function tri-states outputs

- Low jitter 15 ps one sigma

ICS670-03 Applications

- Packaged in 16-pin SOIC