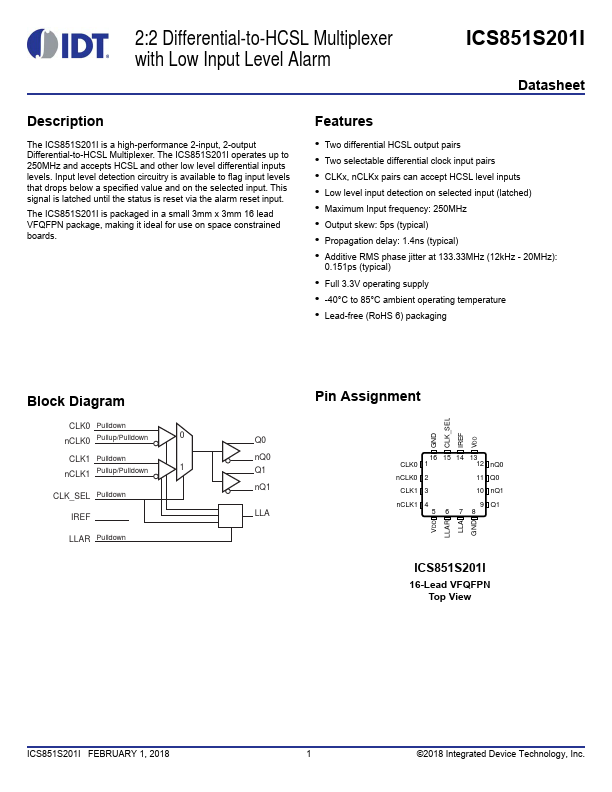

ICS851S201I Key Features

- Two differential HCSL output pairs

- Two selectable differential clock input pairs

- CLKx, nCLKx pairs can accept HCSL level inputs

- Low level input detection on selected input (latched)

- Maximum Input frequency: 250MHz

- Output skew: 5ps (typical)

- Propagation delay: 1.4ns (typical)

- Additive RMS phase jitter at 133.33MHz (12kHz

- 20MHz)