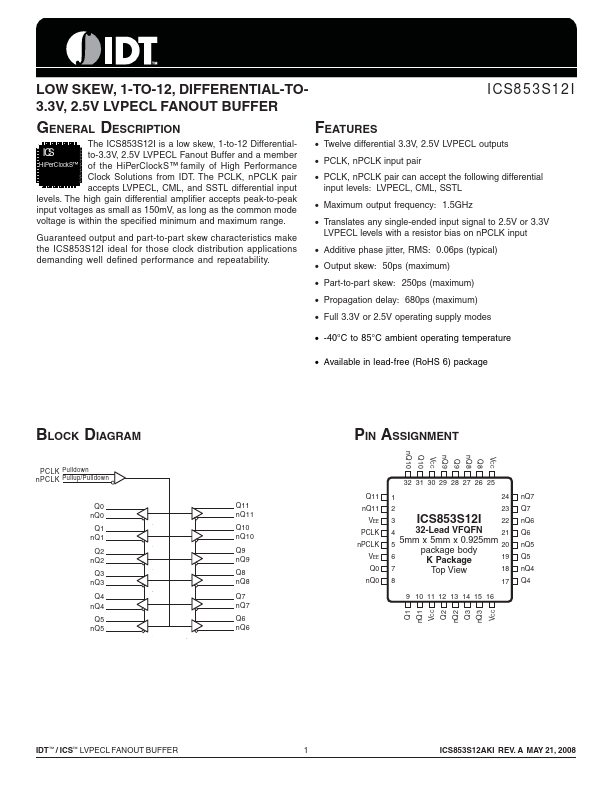

ICS853S12I Key Features

- Twelve differential 3.3V, 2.5V LVPECL outputs

- PCLK, nPCLK input pair

- PCLK, nPCLK pair can accept the following differential input levels: LVPECL, CML, SSTL

- Maximum output frequency: 1.5GHz

- Translates any single-ended input signal to 2.5V or 3.3V