Datasheet Summary

12:2, Differential-to-LVDS Multiplexer

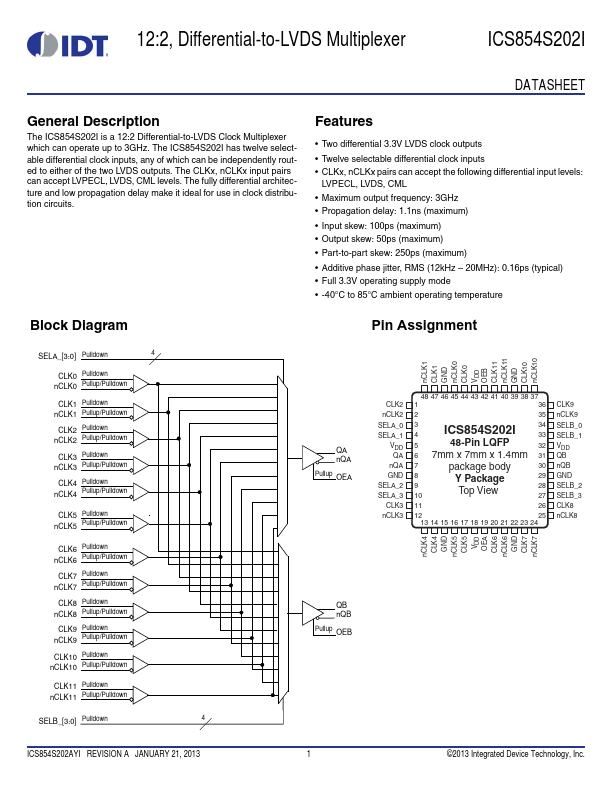

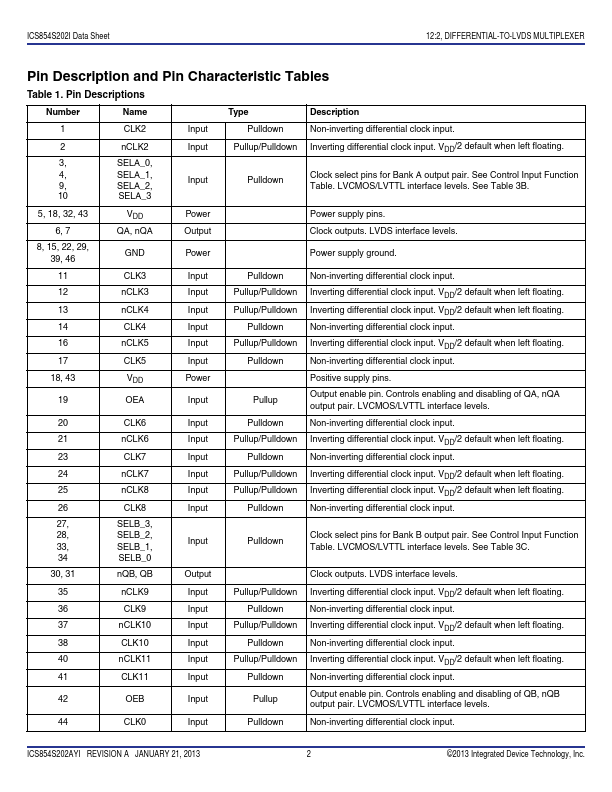

General Description

The ICS854S202I is a 12:2 Differential-to-LVDS Clock Multiplexer which can operate up to 3GHz. The ICS854S202I has twelve selectable differential clock inputs, any of which can be independently routed to either of the two LVDS outputs. The CLKx, nCLKx input pairs can accept LVPECL, LVDS, CML levels. The fully differential architecture and low propagation delay make it ideal for use in clock distribution circuits.

Features

- Two differential 3.3V LVDS clock outputs

- Twelve selectable differential clock inputs

- CLKx, nCLKx pairs can accept the following differential input levels:

LVPECL, LVDS, CML

-...