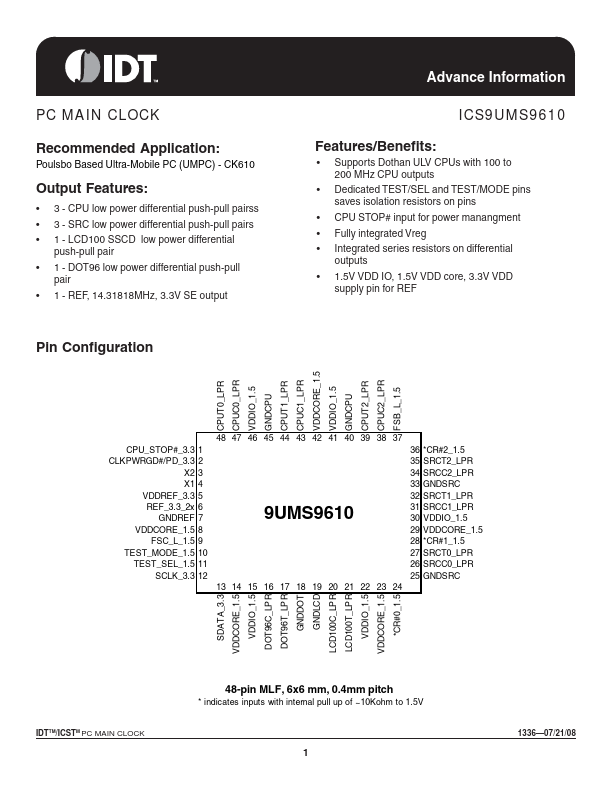

ICS9UMS9610 Description

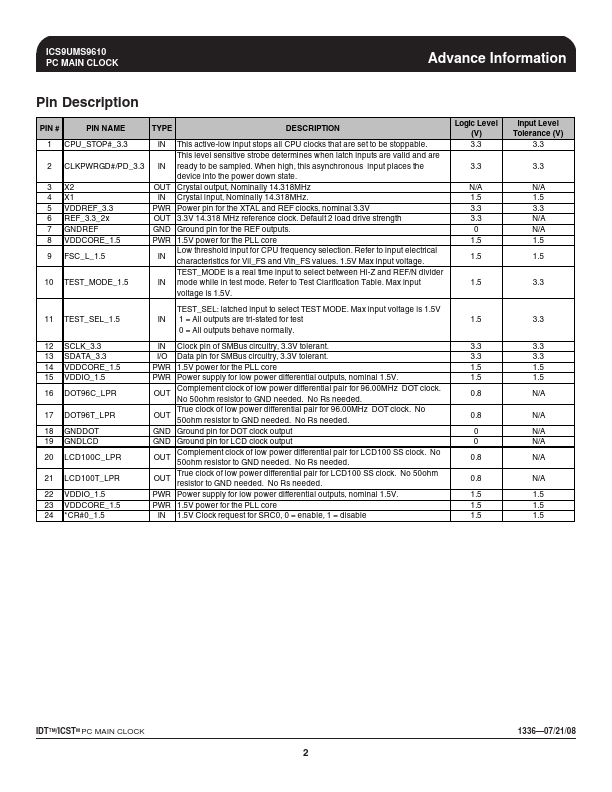

PIN # PIN NAME TYPE DESCRIPTION 1 CPU_STOP#_3.3 IN This active-low input stops all CPU clocks that are set to be stoppable. This level sensitive strobe determines when latch inputs are valid and are 2 CLKPWRGD#/PD_3.3 IN ready to be sampled. When high, this asynchronous input places the device into the power down state.

ICS9UMS9610 Key Features

- CPU low power differential push-pull pairss

- SRC low power differential push-pull pairs

- LCD100 SSCD low power differential

- DOT96 low power differential push-pull

- REF, 14.31818MHz, 3.3V SE output