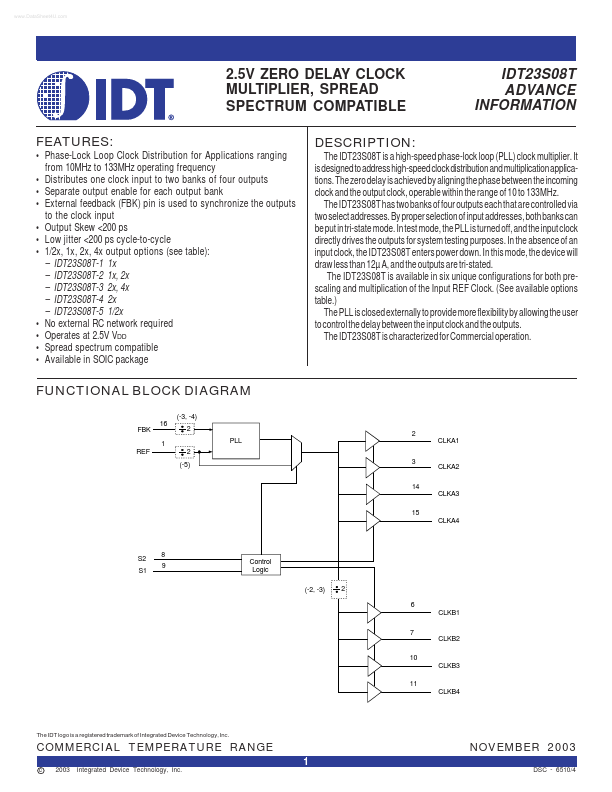

- Part: IDT23S08T

- Description: 2.5V ZERO DELAY CLOCK MULTIPLIER

- Manufacturer: IDT

- Size: 76.82 KB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

| IDT23S09 | Renesas | 3.3V ZERO DELAY CLOCK BUFFER |

| IDT23S05E | Renesas | 3.3V ZERO DELAY CLOCK BUFFER |

| IDT23S05T | Renesas | 2.5V ZERO DELAY CLOCK BUFFER |