IDT54FCT299AT Description

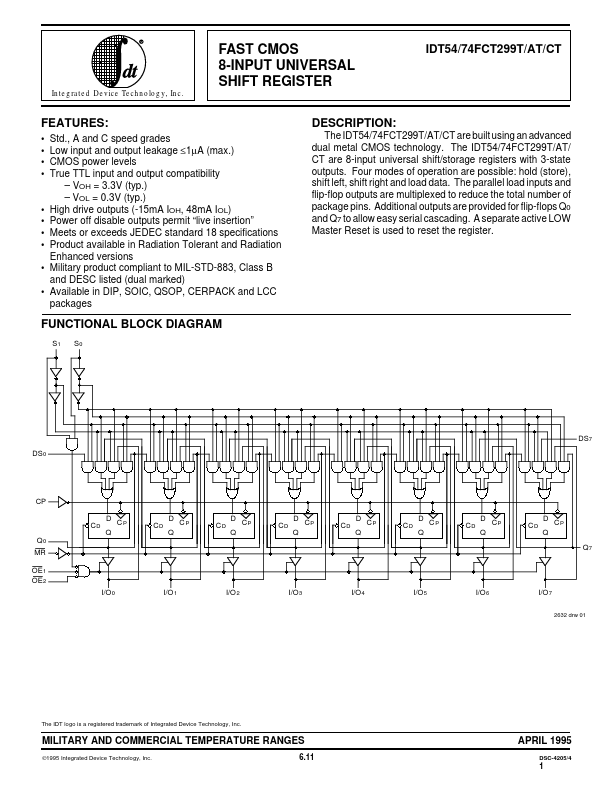

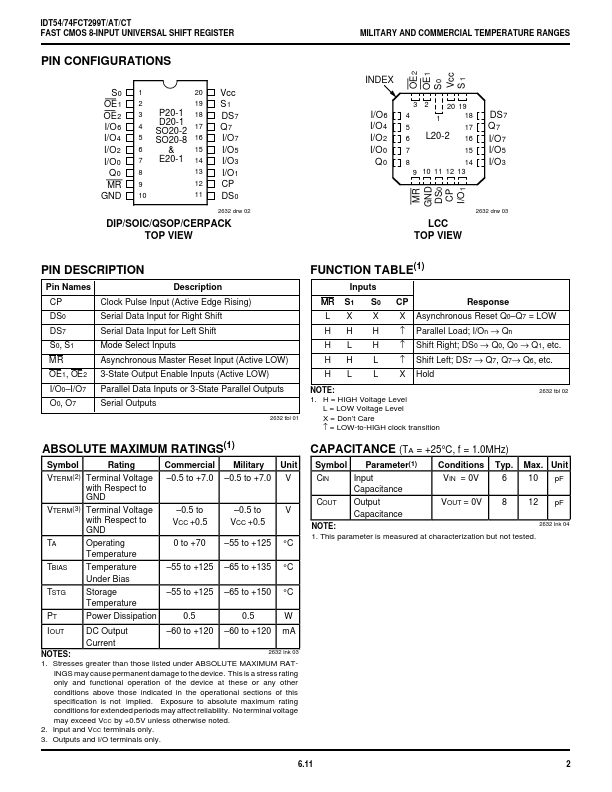

The IDT54/74FCT299T/AT/CT are built using an advanced dual metal CMOS technology. The IDT54/74FCT299T/AT/ CT are 8-input universal shift/storage registers with 3-state outputs. Four modes of operation are possible:.

IDT54FCT299AT Key Features

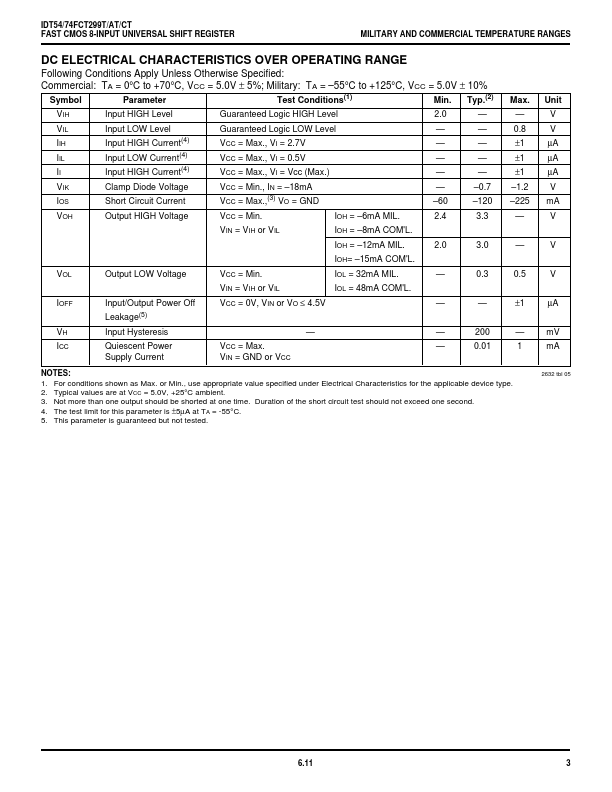

- Std., A and C speed grades

- Low input and output leakage ≤1µA (max.)

- CMOS power levels

- True TTL input and output patibility

- VOH = 3.3V (typ.)

- VOL = 0.3V (typ.)

- High drive outputs (-15mA IOH, 48mA IOL)

- Power off disable outputs permit “live insertion”

- Meets or exceeds JEDEC standard 18 specifications

- Product available in Radiation Tolerant and Radiation Enhanced versions