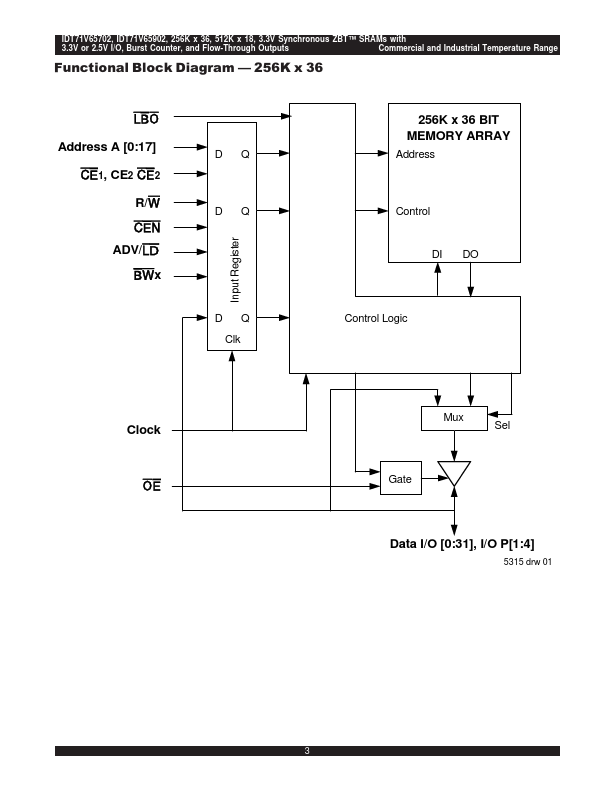

IDT71V65702 Description

They are designed to eliminate dead bus cycles when turning the bus around between reads and writes, or writes and reads. Thus they have been given the name ZBTTM, or Zero Bus Turnaround. Address and control signals are applied to the SRAM during one clock cycle, and on the next clock cycle the associated data cycle occurs, be it read or write.

IDT71V65702 Key Features

- 100 MHz (7.5 ns Clock-to-Data Access) ZBTTM Feature