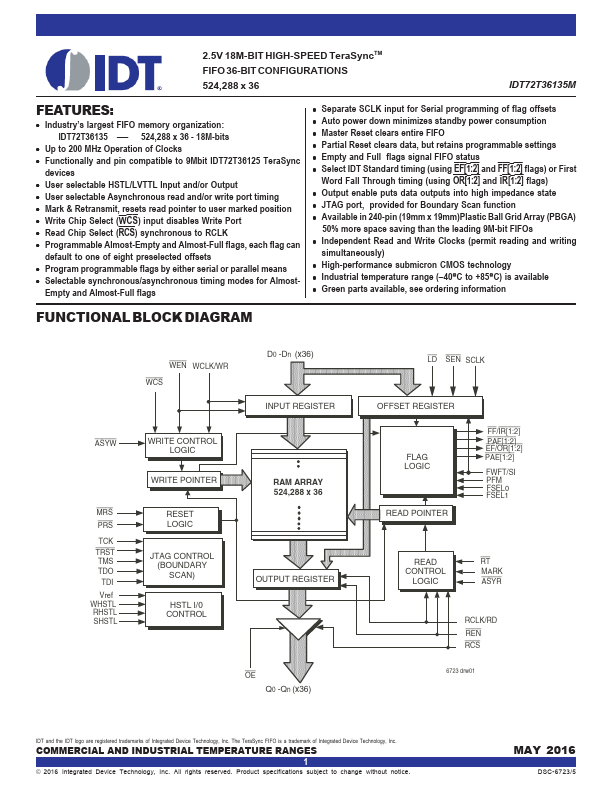

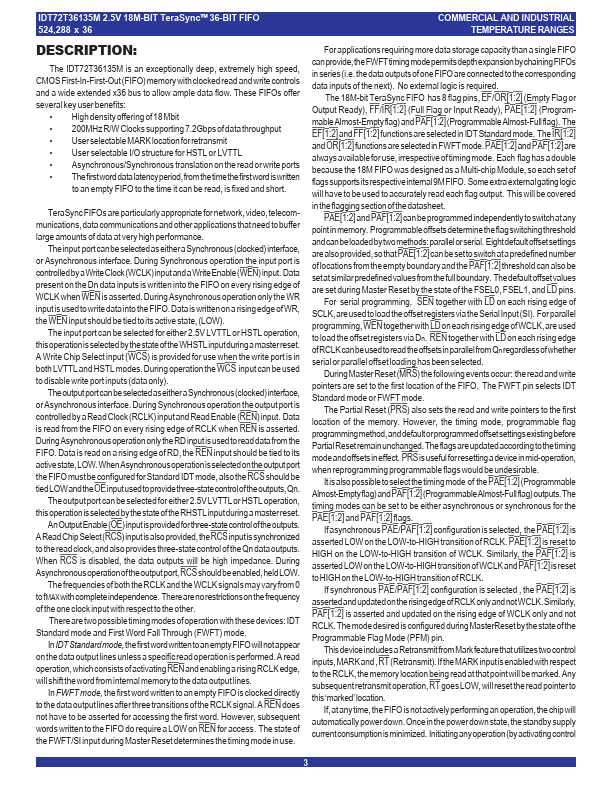

IDT72T36135M Description

2.5V 18M-BIT HIGH-SPEED TeraSyncTM FIFO 36-BIT CONFIGURATIONS 524,288 x 36 IDT72T36135M.

IDT72T36135M Key Features

- Industry’s largest FIFO memory organization: IDT72T36135 ⎯ 524,288 x 36

- 18M-bits

- Up to 200 MHz Operation of Clocks

- Functionally and pin patible to 9Mbit IDT72T36125 TeraSync

- User selectable HSTL/LVTTL Input and/or Output

- User selectable Asynchronous read and/or write port timing

- Mark & Retransmit, resets read pointer to user marked position

- Write Chip Select (WCS) input disables Write Port

- Read Chip Select (RCS) synchronous to RCLK

- Programmable Almost-Empty and Almost-Full flags, each flag can