Datasheet Summary

..

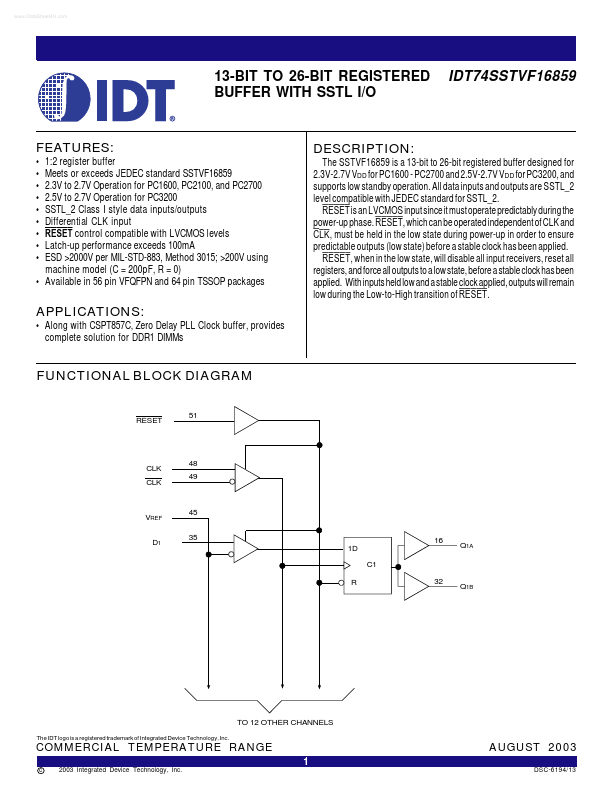

IDT74SSTVF16859 13-BIT TO 26-BIT REGISTERED BUFFER WITH SSTL I/O

MERCIAL TEMPERATURE RANGE

13-BIT TO 26-BIT REGISTERED BUFFER WITH SSTL I/O

Features

:

- -

- -

- -

- -

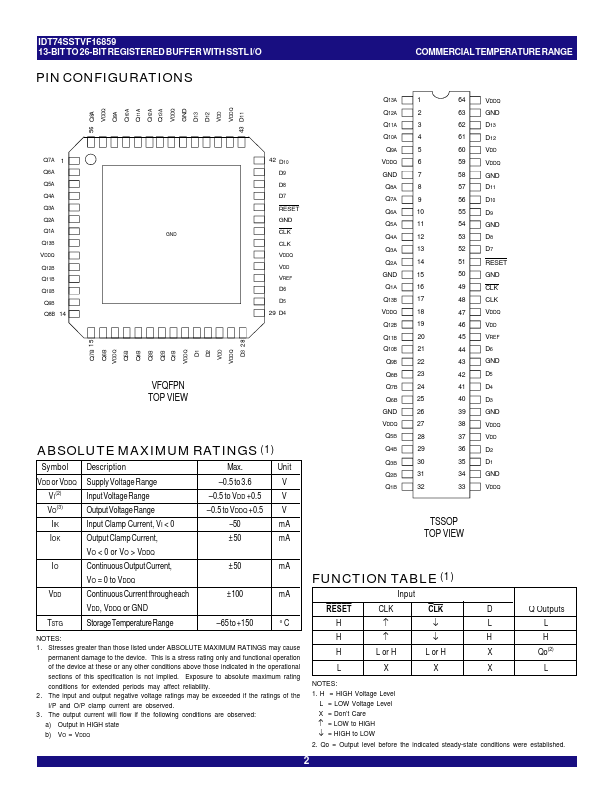

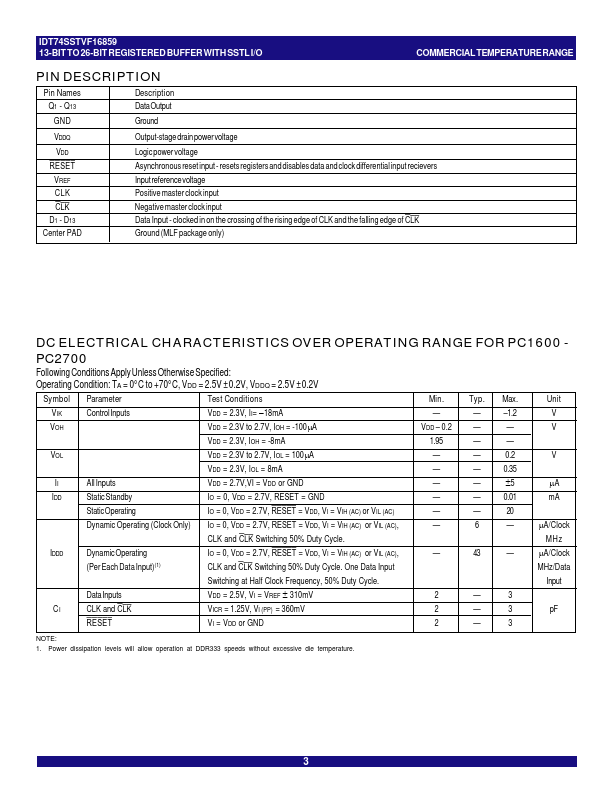

- 1:2 register buffer Meets or exceeds JEDEC standard SSTVF16859 2.3V to 2.7V Operation for PC1600, PC2100, and PC2700 2.5V to 2.7V Operation for PC3200 SSTL_2 Class I style data inputs/outputs Differential CLK input RESET control patible with LVCMOS levels Latch-up performance exceeds 100mA ESD >2000V per MIL-STD-883, Method 3015; >200V using machine model (C = 200pF, R = 0)

- Available in 56 pin VFQFPN and 64 pin TSSOP packages

The SSTVF16859 is a 13-bit to 26-bit registered...