IDT85304-01

IDT85304-01 is 1-TO-5 DIFFERENTIAL-TO-3.3V LVPECL FANOUT BUFFER manufactured by IDT.

..

IDT85304-01 LOW SKEW, 1-TO-5 DIFFERENTIAL-TO-3.3V LVPECL

MERCIAL AND INDUSTRIAL TEMPERATURE RANGES

LOW SKEW, 1-TO-5 DIFFERENTIAL-TO-3.3V LVPECL FANOUT BUFFER

Features

:

- Five differential 3.3V LVPECL outputs

- Selectable differential CLK, x CLK, or LVPECL clock inputs

- CLK, x CLK pair can accept the following differential input levels: LVDS, LVPECL, LVHSTL, SSTL, and HCSL

- PCLK, x PCLK supports the following input types: LVPECL, CML, and SSTL

- Maximum output frequency: 650MHz

- Translates any single-ended input signal to 3.3V LVPECL levels with resistor bias on x CLK input

- Output skew: 35ps (max.)

- Part-to-part skew: as low as 150ps

- Propagation delay: 2.1ns (max.)

- 3.3V operating supply

- Available in TSSOP package

DESCRIPTION:

The IDT85304-01 is a low skew, high performance 1-to-5 differential-to3.3V LVPECL clock generator-divider. It has two selectable clock inputs. The CLK/ x CLK pair can accept most standard differential input levels. The PCLK/ x PCLK pair can accept LVPECL, CML, or SSTL input levels. The clock enable is internally synchronized to eliminate runt pulses on the outputs during asynchronous assertion/deassertion of the clock enable pin. Guaranteed output and part-to-part skew characteristics make the IDT8530401 ideal for those applications that demand well-defined performance and repeatability.

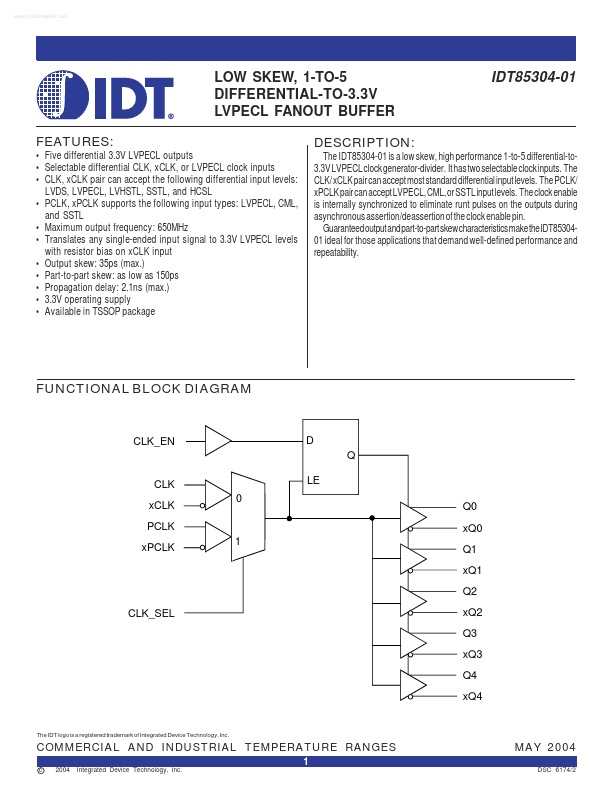

FUNCTIONAL BLOCK DIAGRAM

CLK_EN

CLK x CLK PCLK x PCLK 1 0

LE Q0 x Q0 Q1 x Q1 Q2

CLK_SEL x Q2 Q3 x Q3 Q4 x Q4

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

MERCIAL AND INDUSTRIAL TEMPERATURE RANGES

1 c 2004 Integrated Device Technology, Inc.

MAY 2004

DSC 6174/2

IDT85304-01 LOW SKEW, 1-TO-5 DIFFERENTIAL-TO-3.3V...