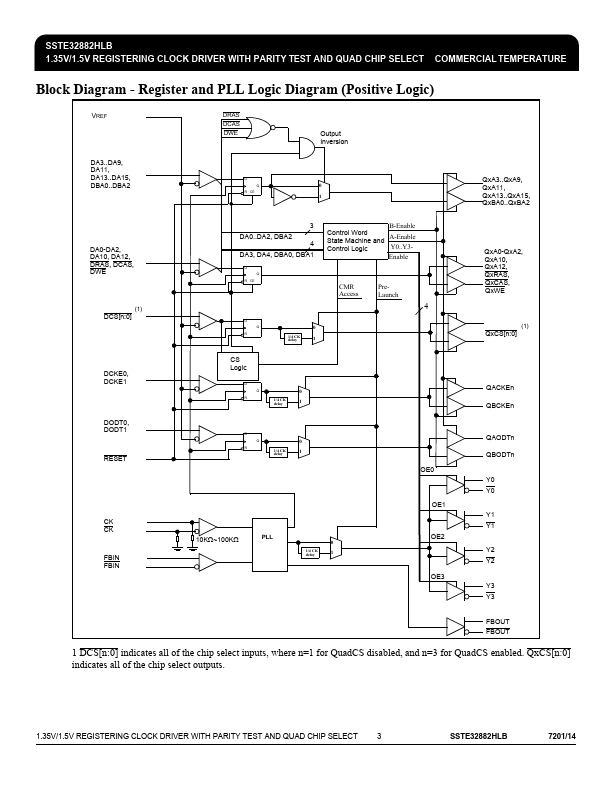

SSTE32882HLB Description

All inputs are 1.35V and 1.5V CMOS patible, except the reset (RESET) and MIRROR inputs which are LVCMOS. All outputs are 1.35V and 1.5V CMOS edge-controlled drivers optimized to drive single terminated 25 to 50 traces in DDR3 RDIMM applications, except the open-drain error (ERROUT) output. The clock outputs (Yn and Yn) and control net outputs QnCKEn, QnCSn and QnODTn are designed with a different strength and skew...