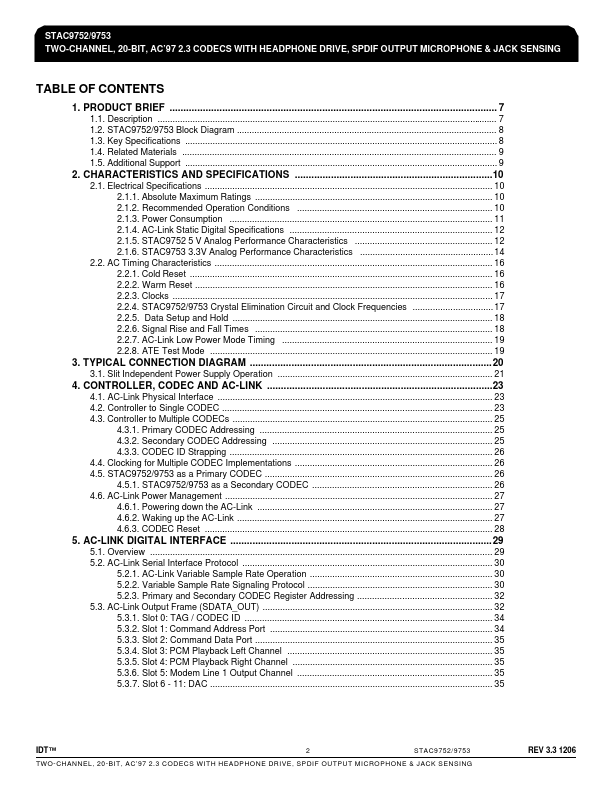

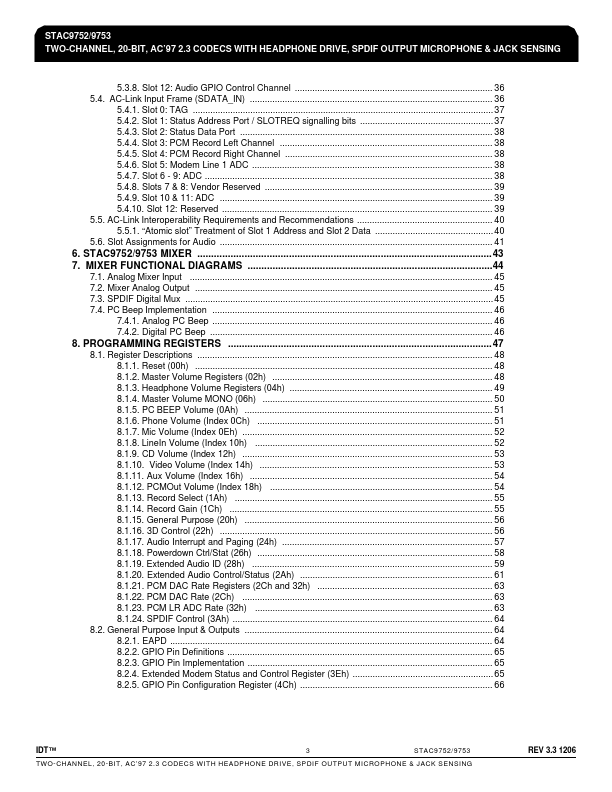

STAC9753 Description

IDT's STAC9752/9753 are general purpose 20-bit, full duplex, audio CODECs conforming to the analog ponent specification of AC'97 (Audio CODEC 97 ponent Specification Rev. The STAC9752/9753 incorporate IDT's proprietary Σ∆ technology to achieve a DAC SNR in excess of 90dB. The DACs, ADCs and mixer are integrated with analog I/Os, which include four analog line-level stereo inputs, two analog line-level mono inputs,...

STAC9753 Key Features

- High performance Σ∆ technology AC’97 Rev 2.3 pliant 20-bit full duplex stereo ADCs, DACs Independent sample rates for AD