IS42S32400E Key Features

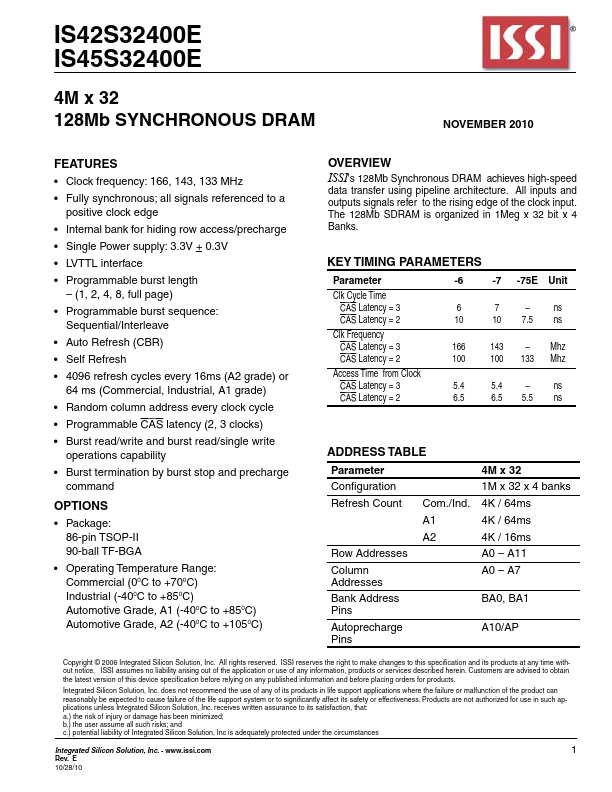

- Clock frequency: 166, 143, 133 MHz

- Fully synchronous; all signals referenced to a positive clock edge

- Internal bank for hiding row access/precharge

- Single Power supply: 3.3V + 0.3V

- LVTTL interface

- Programmable burst length

- (1, 2, 4, 8, full page)

- Programmable burst sequence: Sequential/Interleave

- Auto Refresh (CBR)

- Self Refresh