IS43LD16320A Overview

Key Specifications

Package: TFBGA

Operating Voltage: 1.2 V

Max Voltage (typical range): 1.3 V

Min Voltage (typical range): 1.14 V

Description

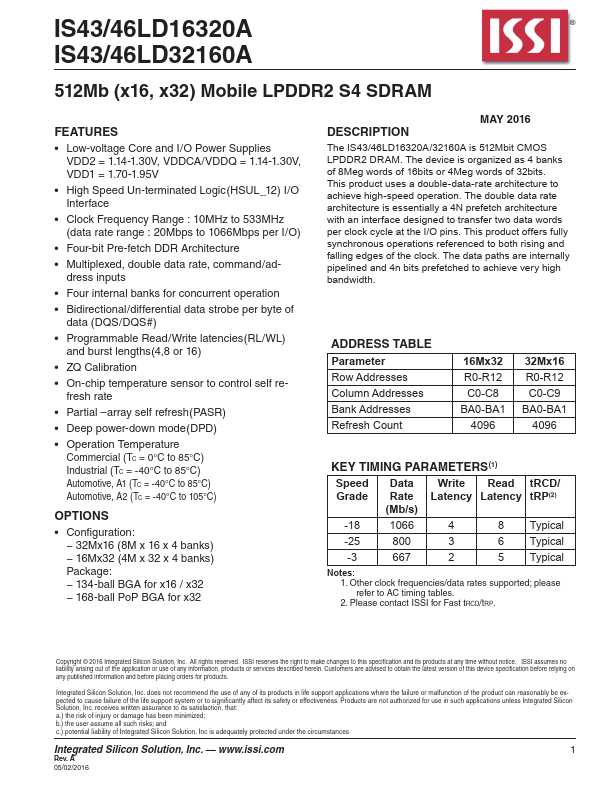

MAY 2016 The IS43/46LD16320A/32160A is 512Mbit CMOS LPDDR2 DRAM. The device is organized as 4 banks of 8Meg words of 16bits or 4Meg words of 32bits.

Key Features

- Low-voltage Core and I/O Power Supplies VDD2 = 1.14-1.30V, VDDCA/VDDQ = 1.14-1.30V, VDD1 = 1.70-1.95V

- High Speed Un-terminated Logic(HSUL_12) I/O Interface

- Clock Frequency Range : 10MHz to 533MHz (data rate range : 20Mbps to 1066Mbps per I/O)

- Four-bit Pre-fetch DDR Architecture

- Multiplexed, double data rate, command/address inputs