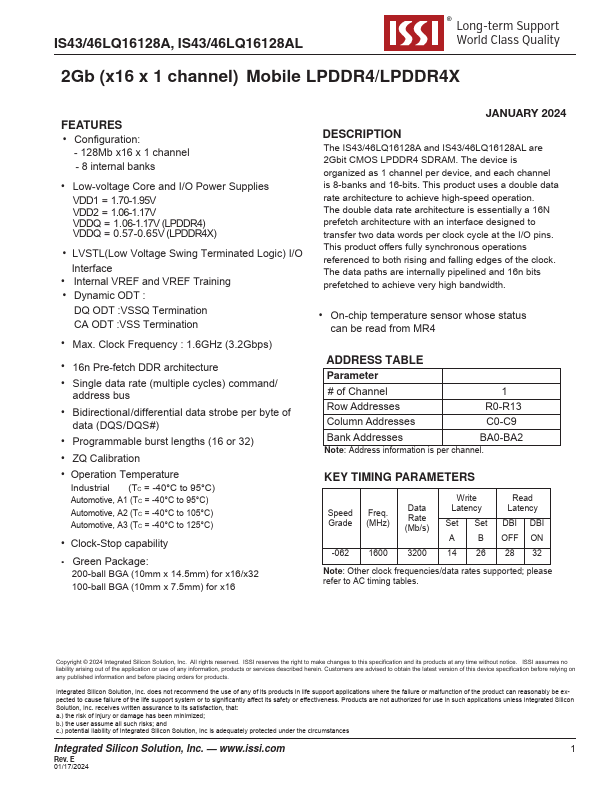

IS43LQ16128AL Overview

Key Specifications

Max Voltage (typical range): 1.95 V

Min Voltage (typical range): 1.7 V

Max Frequency: 1.6 GHz

Length: 14.5 mm

Description

The IS43/46LQ16128A and IS43/46LQ16128AL are 2Gbit CMOS LPDDR4 SDRAM. The device is organized as 1 channel per device, and each channel is 8-banks and 16-bits.

Key Features

- Configuration

- 128Mb x16 x 1 channel

- 8 internal banks

- LVSTL(Low Voltage Swing Terminated Logic) I/O Interface

- Internal VREF and VREF Training