IS43LR32640B Overview

Key Specifications

Package: TFBGA

Operating Voltage: 1.8 V

Max Voltage (typical range): 1.95 V

Min Voltage (typical range): 1.7 V

Description

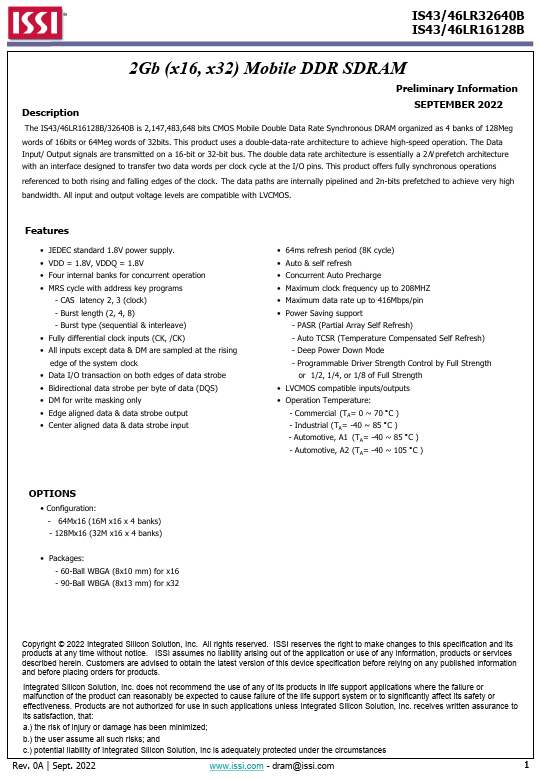

SEPTEMBER 2022 The IS43/46LR16128B/32640B is 2,147,483,648 bits CMOS Mobile Double Data Rate Synchronous DRAM organized as 4 banks of 128Meg words of 16bits or 64Meg words of 32bits. This product uses a double-data-rate architecture to achieve high-speed operation.

Key Features

- JEDEC standard 1.8V power supply

- VDD = 1.8V, VDDQ = 1.8V

- Four internal banks for concurrent operation

- MRS cycle with address key programs

- CAS latency 2, 3 (clock)