IS46LQ16256AL Overview

Description

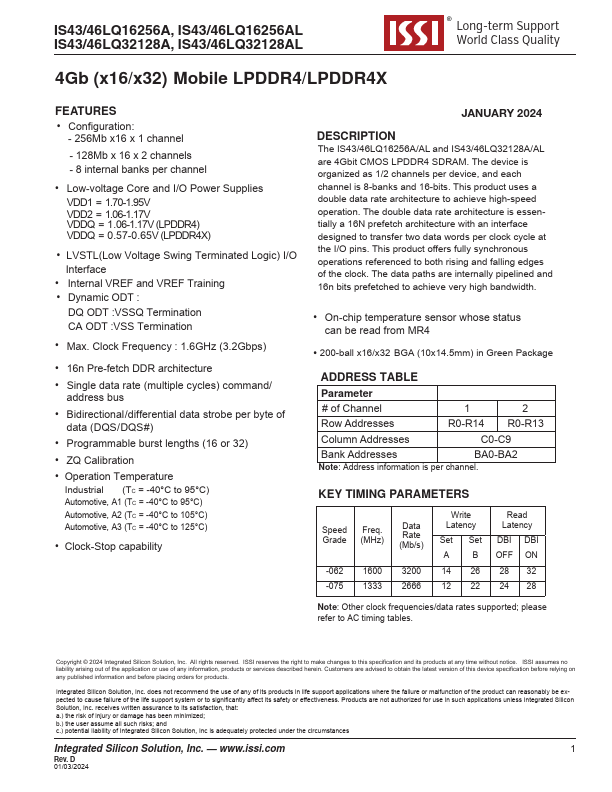

The IS43/46LQ16256A/AL and IS43/46LQ32128A/AL are 4Gbit CMOS LPDDR4 SDRAM. The device is organized as 1/2 channels per device, and each channel is 8-banks and 16-bits.

Key Features

- Configuration

- 256Mb x16 x 1 channel

- 128Mb x 16 x 2 channels

- 8 internal banks per channel

- LVSTL(Low Voltage Swing Terminated Logic) I/O Interface

- Internal VREF and VREF Training

- Dynamic ODT : DQ ODT :VSSQ Termination CA ODT :VSS Termination

- Max. Clock Frequency : 1.6GHz (3.2Gbps)

- 16n Pre-fetch DDR architecture

- Single data rate (multiple cycles) command/ address bus