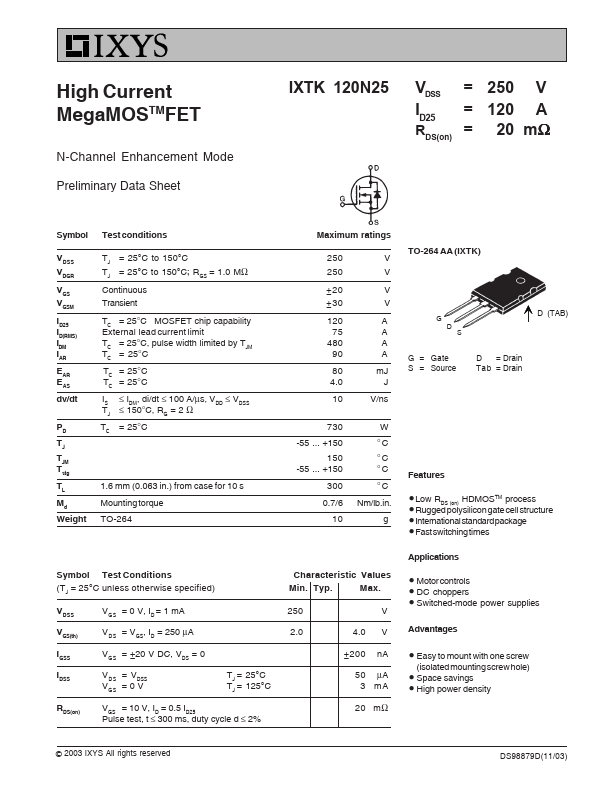

IXTN120N25

Key Features

- Low RDS (on) HDMOSTM process

- Rugged polysilicon gate cell structure

- Internationalstandardpackage

- Fast switching times Symbol Test Conditions (TJ = 25°C unless otherwise specified) VDSS VGS = 0 V, ID = 1 mA VGS(th) VDS = VGS, ID = 250 µA IGSS VGS = ±20 V DC, VDS = 0 IDSS VDS = VDSS VGS = 0 V TJ = 25°C TJ = 125°C RDS(on) VPuGSlse=te1s0t,Vt,≤ID3=000.m5 sID,2d5 uty cycle d ≤ 2% Characteristic Values Min. Typ. Max. 250 V

- 0 4.0 V ±200 nA 50 µA 3 mA 20 mΩ