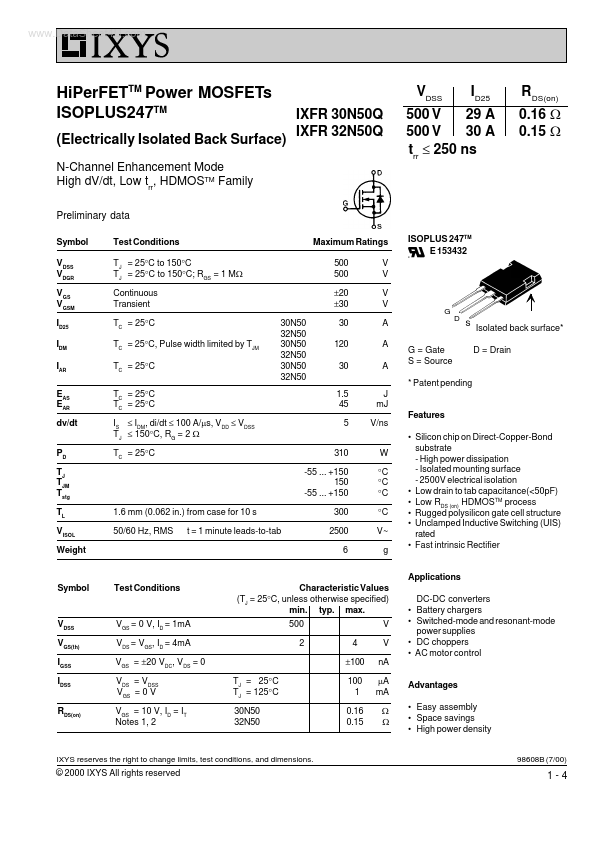

32N50Q

Key Features

- Silicon chip on Direct-Copper-Bond substrate - High power dissipation - Isolated mounting surface - 2500V electrical isolation

- Low drain to tab capacitance(<50pF)

- Low RDS (on) HDMOSTM process

- Rugged polysilicon gate cell structure

- Unclamped Inductive Switching (UIS) rated

- Fast intrinsic Rectifier