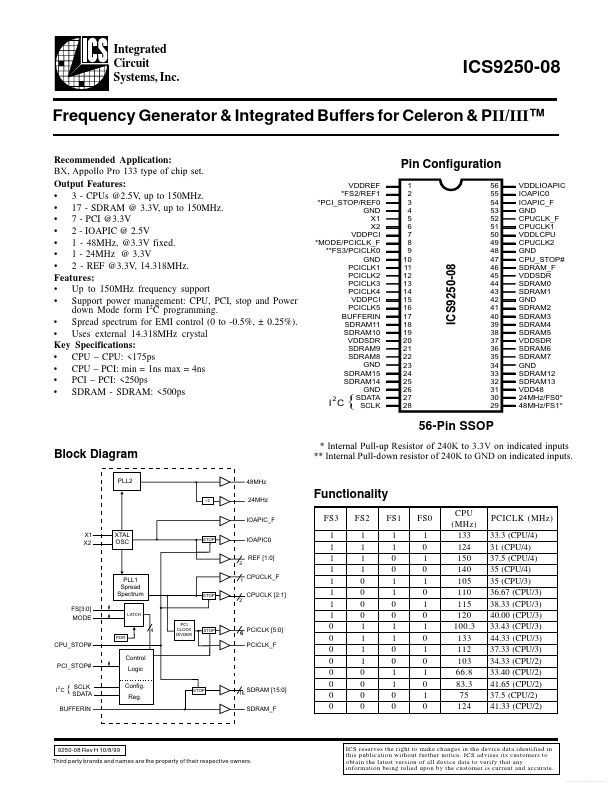

9250-08 Overview

Key Features

- 3 - CPUs @2.5V, up to 150MHz

- 17 - SDRAM @ 3.3V, up to 150MHz

- 7 - PCI @3.3V

- 2 - IOAPIC @ 2.5V

- 1 - 48MHz, @3.3V fixed

- 1 - 24MHz @ 3.3V

- 2 - REF @3.3V, 14.318MHz. Features

- Up to 150MHz frequency support

- Support power management: CPU, PCI, stop and Power down Mode form I2C programming

- Spread spectrum for EMI control (0 to -0.5%, ± 0.25%)