ICS650-01B Description

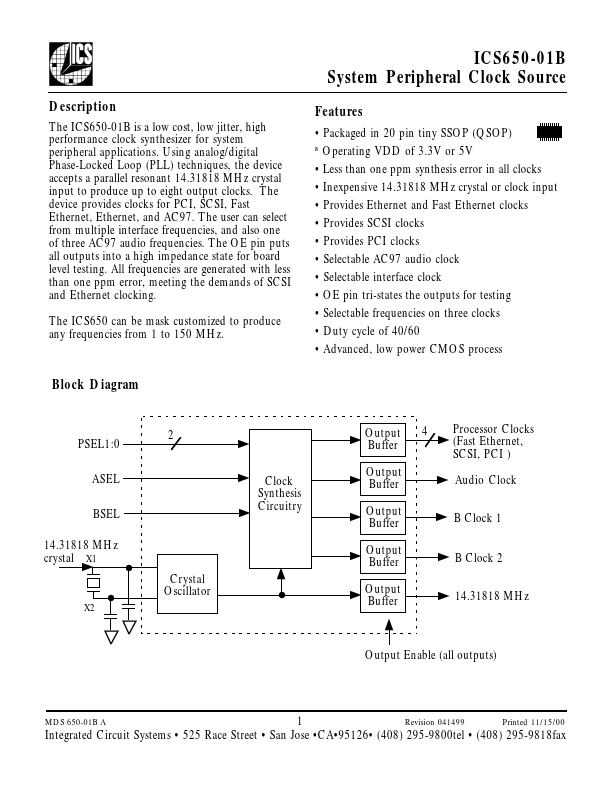

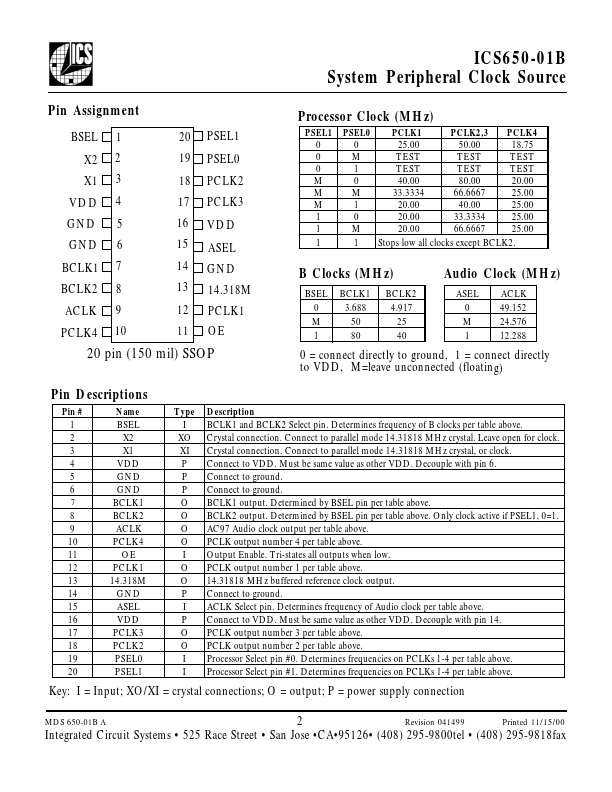

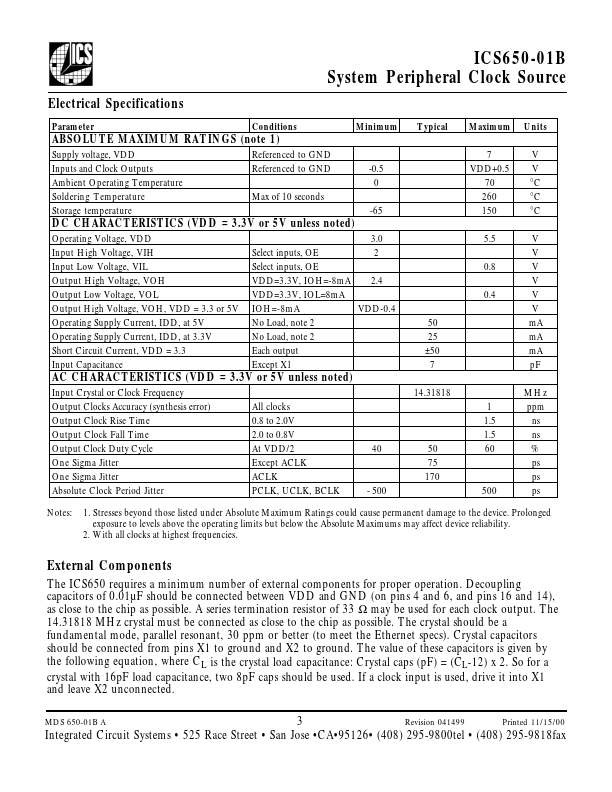

The ICS650-01B is a low cost, low jitter, high performance clock synthesizer for system peripheral applications. Using analog/digital Phase-Locked Loop (PLL) techniques, the device accepts a parallel resonant 14.31818 MHz crystal input to produce up to eight output clocks. The device provides clocks for PCI, SCSI, Fast Ethernet, Ethernet, and AC97.

ICS650-01B Applications

- Packaged in 20 pin tiny SSOP (QSOP) ª Operating VDD of 3.3V or 5V

- Less than one ppm synthesis error in all clocks