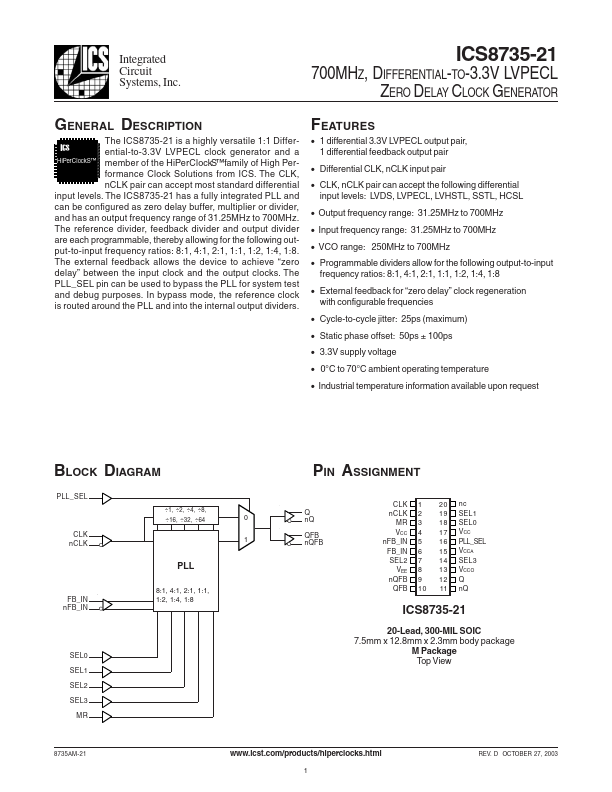

ICS8735-21

Description

The ICS8735-21 is a highly versatile 1:1 Differential-to-3.3V LVPECL clock generator and a HiPerClockS™ member of the HiPerClockS™family of High Performance Clock Solutions from ICS.

Key Features

- 1 differential 3.3V LVPECL output pair, 1 differential feedback output pair

- Differential CLK, nCLK input pair

- CLK, nCLK pair can accept the following differential input levels: LVDS, LVPECL, LVHSTL, SSTL, HCSL

- Output frequency range: 31.25MHz to 700MHz

- Input frequency range: 31.25MHz to 700MHz

- VCO range: 250MHz to 700MHz

- External feedback for “zero delay” clock regeneration with configurable frequencies

- Cycle-to-cycle jitter: 25ps (maximum)

- Static phase offset: 50ps ± 100ps

- 3.3V supply voltage