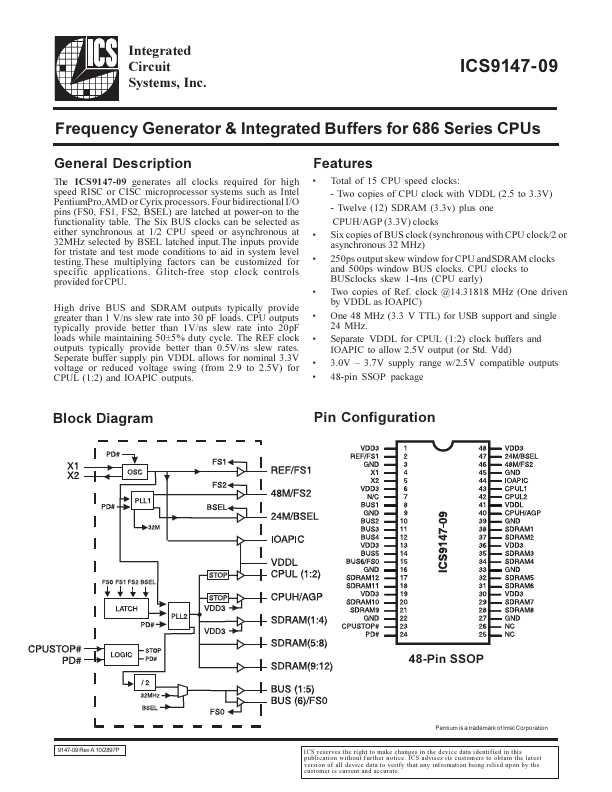

| Part | ICS9147-09 |

|---|---|

| Description | Frequency Generator & Integrated Buffers |

| Manufacturer | Integrated Circuit Systems |

| Size | 601.92 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| LM13600 | National Semiconductor | Dual Operational Transconductance Amplifiers with Linearizing Diodes and Buffers |

| 7406 | System Logic Semiconductor | Hex Inverted Buffers |

| CD4049A | RCA Solid State | CMOS HEX BUFFERS/CONVERTERS |