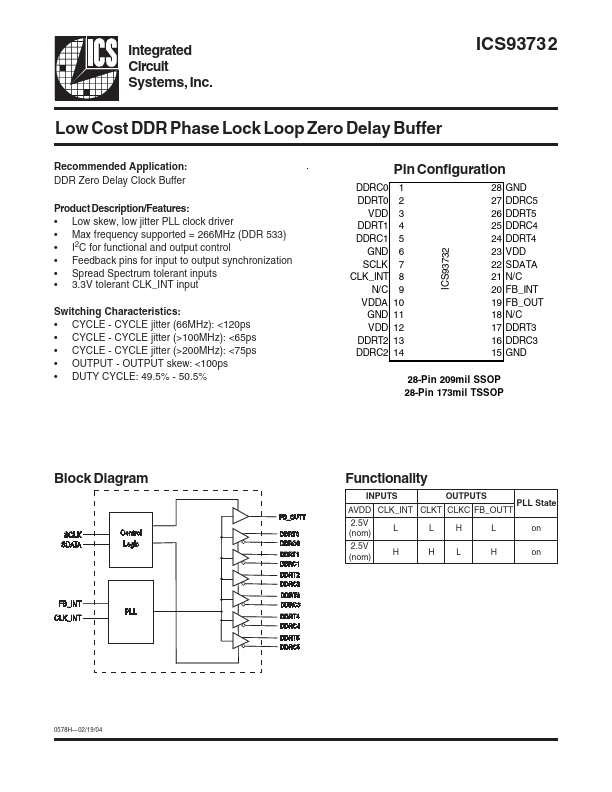

ICS93732 Description

/.

ICS93732 Key Features

- Low skew, low jitter PLL clock driver

- Max frequency supported = 266MHz (DDR 533)

- I2C for functional and output control

- Feedback pins for input to output synchronization

- Spread Spectrum tolerant inputs

- 3.3V tolerant CLK_INT input

- CYCLE jitter (66MHz): <120ps

- CYCLE jitter (>100MHz): <65ps

- CYCLE jitter (>200MHz): <75ps

- OUTPUT