MK3805

Overview

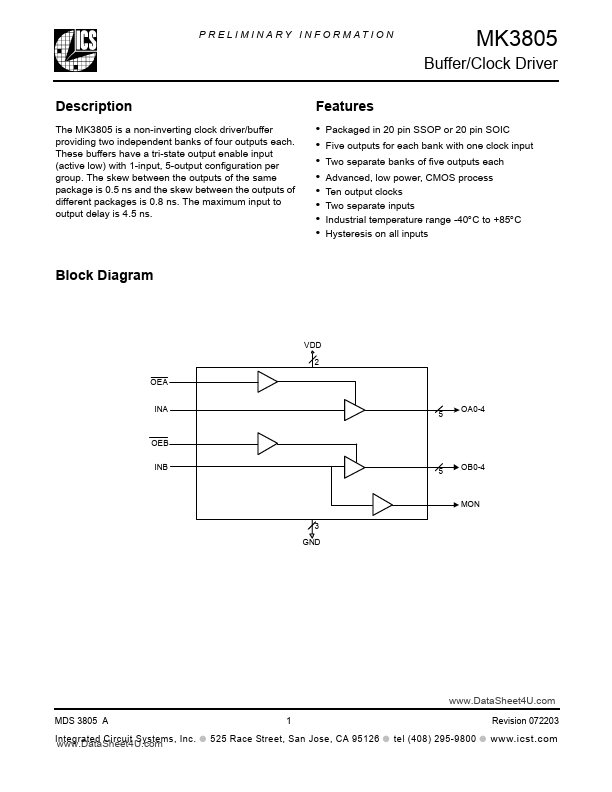

The MK3805 is a non-inverting clock driver/buffer providing two independent banks of four outputs each. These buffers have a tri-state output enable input (active low) with 1-input, 5-output configuration per group.

- Packaged in 20 pin SSOP or 20 pin SOIC Five outputs for each bank with one clock input Two separate banks of five outputs each Advanced, low power, CMOS process Ten output clocks Two separate inputs Industrial temperature range -40°C to +85°C Hysteresis on all inputs