IDT49C465

IDT49C465 is 32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT manufactured by Integrated Device.

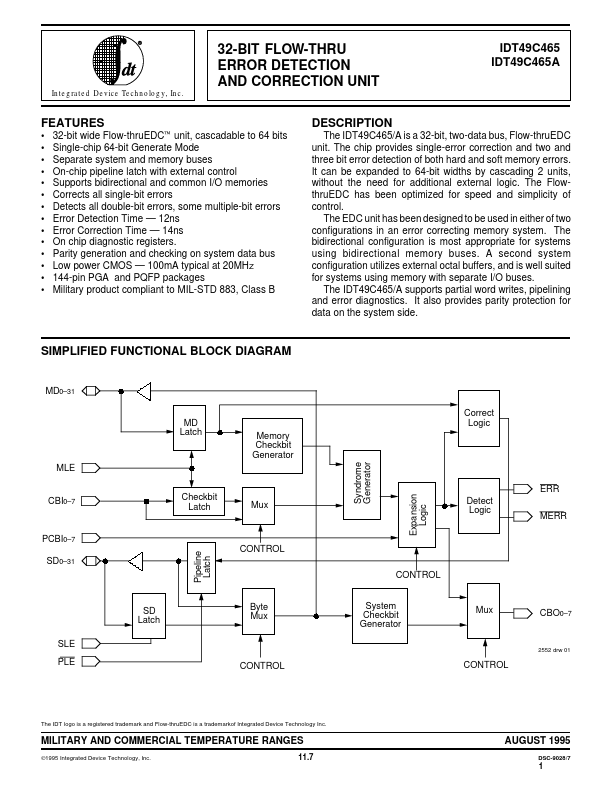

32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT

Integrated Device Technology, Inc.

IDT49C465 IDT49C465A

Features

- -

- -

- -

- -

- -

- -

- -

32-bit wide Flow-thruEDC™ unit, cascadable to 64 bits Single-chip 64-bit Generate Mode Separate system and memory buses On-chip pipeline latch with external control Supports bidirectional and mon I/O memories Corrects all single-bit errors Detects all double-bit errors, some multiple-bit errors Error Detection Time

- 12ns Error Correction Time

- 14ns On chip diagnostic registers. Parity generation and checking on system data bus Low power CMOS

- 100mA typical at 20MHZ 144-pin PGA and PQFP packages Military product pliant to MIL-STD 883,...