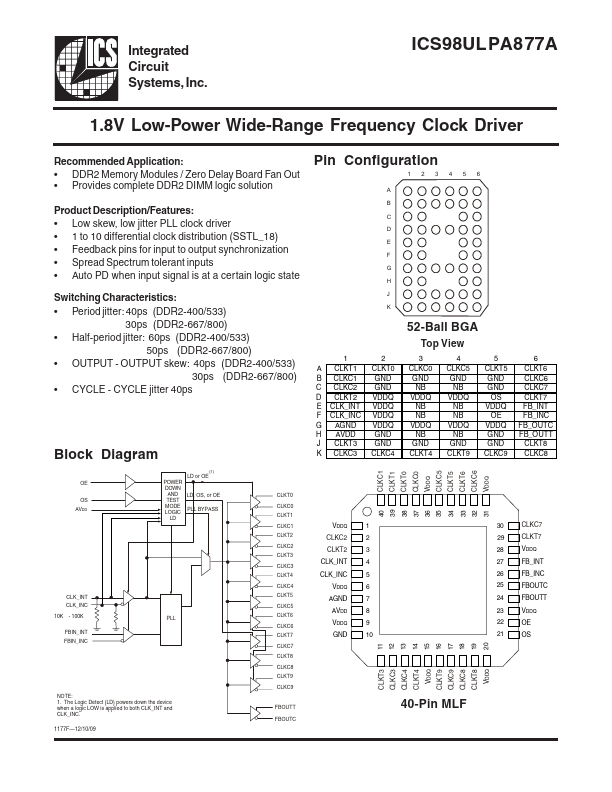

ICS98ULPA877A

Overview

- Low skew, low jitter PLL clock driver

- 1 to 10 differential clock distribution (SSTL_18)

- Feedback pins for input to output synchronization

- Spread Spectrum tolerant inputs

- Auto PD when input signal is at a certain logic state Switching Characteristics:

- Period jitter: 40ps (DDR2-400/533) 30ps (DDR2-667/800)

- Half-period jitter: 60ps (DDR2-400/533) 50ps (DDR2-667/800)

- OUTPUT - OUTPUT skew: 40ps (DDR2-400/533) 30ps (DDR2-667/800)

- CYCLE - CYCLE jitter 40ps