IDT70125S

IDT70125S is HIGH-SPEED 2K x 9 DUAL-PORT STATIC RAM manufactured by Integrated Device Technology.

HIGH-SPEED 2K x 9 DUAL-PORT STATIC RAM WITH BUSY & INTERRUPT

Integrated Device Technology, Inc.

IDT70121S/L IDT70125S/L

Features

:

- High-speed access

- mercial: 25/35/45/55ns (max.)

- Low-power operation

- IDT70121/70125S Active: 500m W (typ.) Standby: 5m W (typ.)

- IDT70121/70125L Active: 500m W (typ.) Standby: 1m W (typ.)

- Fully asychronous operation from either port

- MASTER IDT70121 easily expands data bus width to 18 bits or more using SLAVE IDT70125 chip

- On-chip port arbitration logic (IDT70121 only)

- BUSY output flag on Master; BUSY input on Slave

- INT flag for port-to-port munication

- Battery backup operation- 2V data retention

- TTL-patible, signal 5V (± 10%) power supply

- Available in 52-pin PLCC

- Industrial temperature range (- 40°C to +85°C) is available, tested to military electrical specifications

DESCRIPTION:

The IDT70121/IDT70125 are high-speed 2K x 9 Dual-Port Static RAMs. The IDT70121 is designed to be used as a stand-alone 9-bit Dual-Port RAM or as a “MASTER” Dual-Port RAM together with the IDT70125 “SLAVE” Dual-Port in 18bit-or-more word width systems. Using the IDT MASTER/ SLAVE Dual-Port RAM approach in 18-bit-or-wider memory system applications results in full-speed, error-free operation without the need for additional discrete logic. Both devices provide two independent ports with separate control, address, and I/O pins that permit independent, asynchronous access for reads or writes to any location in memory. An automatic power-down feature, controlled by CE, permits the on-chip circuitry of each port to enter a very low standby power mode. The IDT70121/IDT70125 utilizes a 9-bit wide data path to allow for Data/Control and parity bits at the user’s option. This feature is especially useful in data munications applications where it is necessary to use a parity bit for transmission/reception error checking.

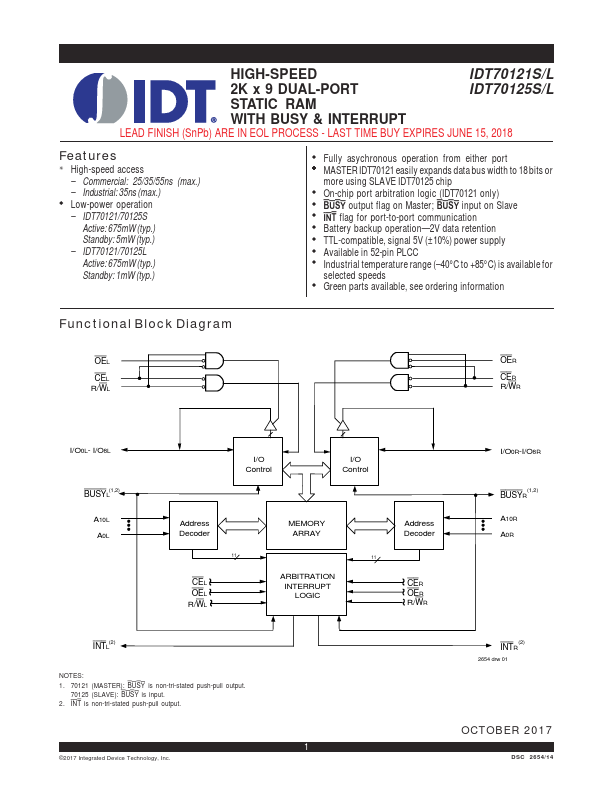

FUNCTIONAL BLOCK DIAGRAM

OE L CE L R/ WL OER

R/WR

I/O0L

- I/O8L I/O Control I/O Control

I/O0R-I/O 8R

BUSY...