IDT71V2558S Description

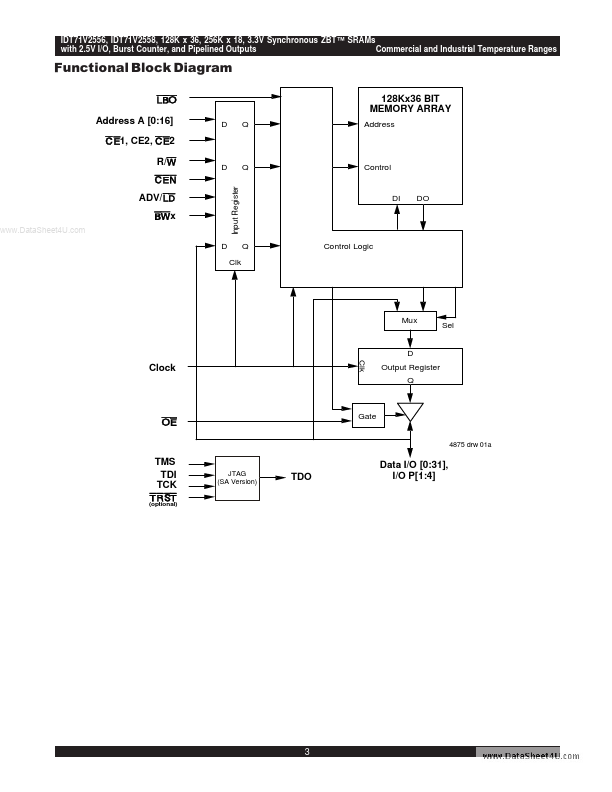

The IDT71V2556/58 are 3.3V high-speed 4,718,592-bit (4.5 Megabit) synchronous SRAMS. They are designed to eliminate dead bus cycles when turning the bus around between reads and writes, or writes and reads. Thus, they have been given the name ZBTTM, or Zero Bus Turnaround.

IDT71V2558S Applications

- BW4) control (May tie active) x Three chip enables for simple depth expansion x 3.3V power supply (±5%), 2.5V I/O Supply (VDDQ) x Optional

- Boundary Scan JTAG Interface (IEEE 1149.1 plaint) x Packaged in a JEDEC standard 100-pin plastic thin quad flatpack (TQFP), 119 ball grid array (BGA) and 165 fi