IP1001

IP1001 is Full Function Synchronous Buck Power Block manufactured by International Rectifier.

- 94336c i P1001

Full Function Synchronous Buck Power Block

Integrated Power Semiconductors, Control IC & Passives

Features

- -

- -

- -

- -

- - 3.3V to 12V input voltage1 20A maximum load capability, with no derating up to TPCB = 90°C 5 bit DAC settable, 0.925V to 2V output voltage range 2 Configurable down to 3.3Vin & up to 3.3Vout with simple external circuit 3 200k Hz or 300k Hz nominal switching frequency Optimized for very low power losses Over & undervoltage protection Adjustable lossless current limit Internal Features minimize layout sensitivity

- Very small outline 14mm x 14mm x 3mm i P1001 Power Block

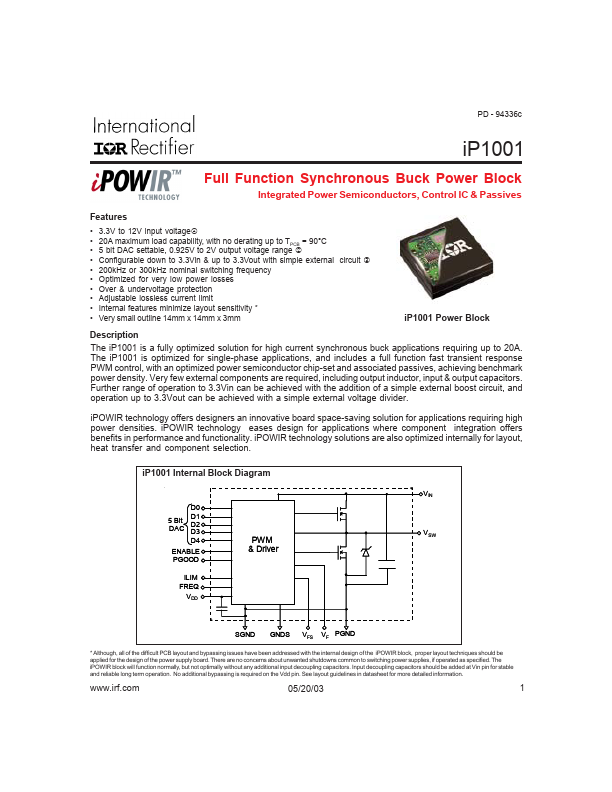

Description The i P1001 is a fully optimized solution for high current synchronous buck applications requiring up to 20A. The i P1001 is optimized for single-phase applications, and includes a full function fast transient response PWM control, with an optimized power semiconductor chip-set and associated passives, achieving benchmark power density. Very few external ponents are required, including output inductor, input & output capacitors. Further range of operation to 3.3Vin can be achieved with the addition of a simple external boost circuit, and operation up to 3.3Vout can be achieved with a simple external voltage divider. i POWIR technology offers designers an innovative board space-saving solution for applications requiring high power densities. i POWIR technology eases design for applications where ponent integration offers benefits in performance and functionality. i POWIR technology solutions are also optimized internally for layout, heat transfer and ponent selection. i P1001 Internal Block Diagram

VIN D0 D1 5 Bit D2 DAC D3 D4 ENABLE PGOOD ILIM FREQ VDD

PWM & Driver

SGND

GNDS

VF PGND

- Although, all of the difficult PCB layout and bypassing issues have been addressed with the internal design of the i POWIR block, proper layout techniques should be applied for the design of the power supply board. There are no concerns about...