IRS2453D Description

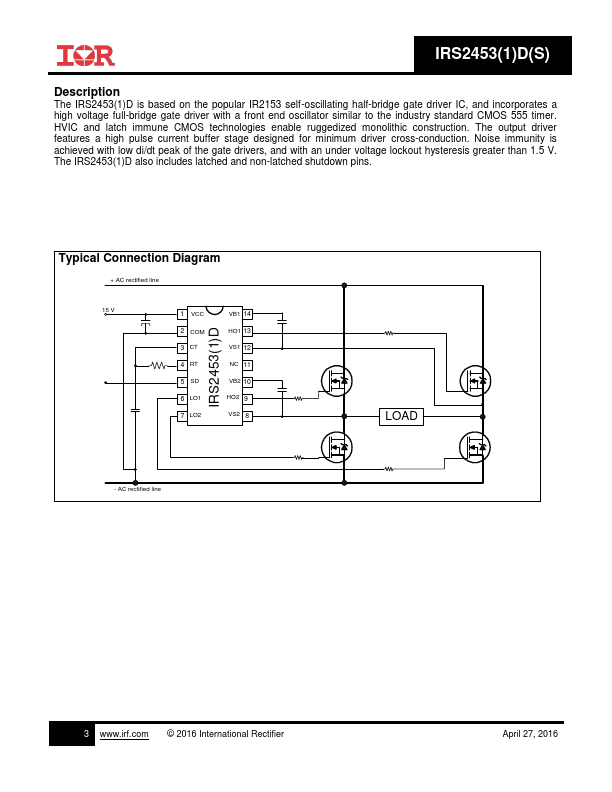

© 2012 International Rectifier November 28, 2012 IRS2453(1)D(S) Description The IRS2453(1)D is based on the popular IR2153 self-oscillating half-bridge gate driver IC, and incorporates a high voltage full-bridge gate driver with a front end oscillator similar to the industry standard CMOS 555 timer. HVIC and latch immune CMOS technologies enable ruggedized monolithic construction.

IRS2453D Key Features

- Integrated 600 V full-bridge gate driver CT, RT programmable oscillator 15.6 V Zener clamp on VCC Micropower startup Log