81C55

81C55 is Radiation Hardened 256 x 8 CMOS RAM manufactured by Intersil.

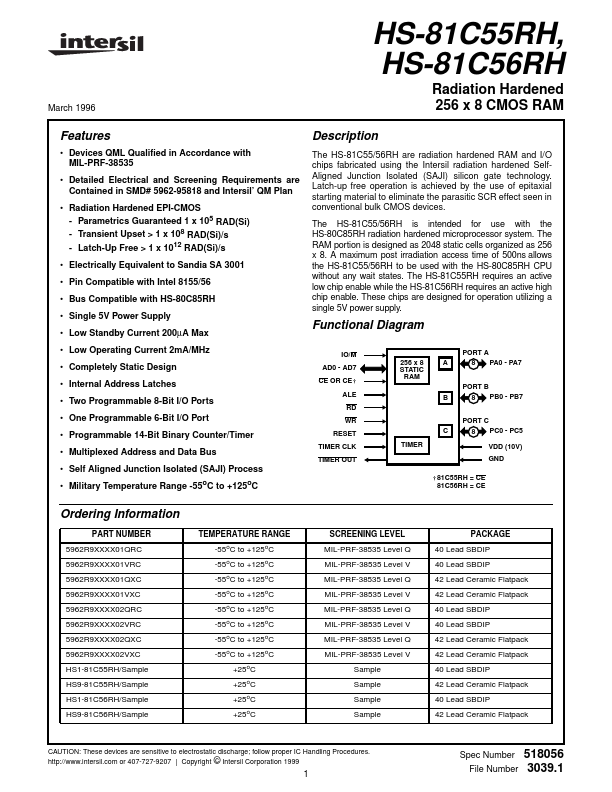

HS-81C55RH, HS-81C56RH

March 1996

Radiation Hardened 256 x 8 CMOS RAM

Description

The HS-81C55/56RH are radiation hardened RAM and I/O chips fabricated using the Intersil radiation hardened SelfAligned Junction Isolated (SAJI) silicon gate technology. Latch-up free operation is achieved by the use of epitaxial starting material to eliminate the parasitic SCR effect seen in conventional bulk CMOS devices. The HS-81C55/56RH is intended for use with the HS-80C85RH radiation hardened microprocessor system. The RAM portion is designed as 2048 static cells organized as 256 x 8. A maximum post irradiation access time of 500ns allows the HS-81C55/56RH to be used with the HS-80C85RH CPU without...