CD40194BMS

Overview

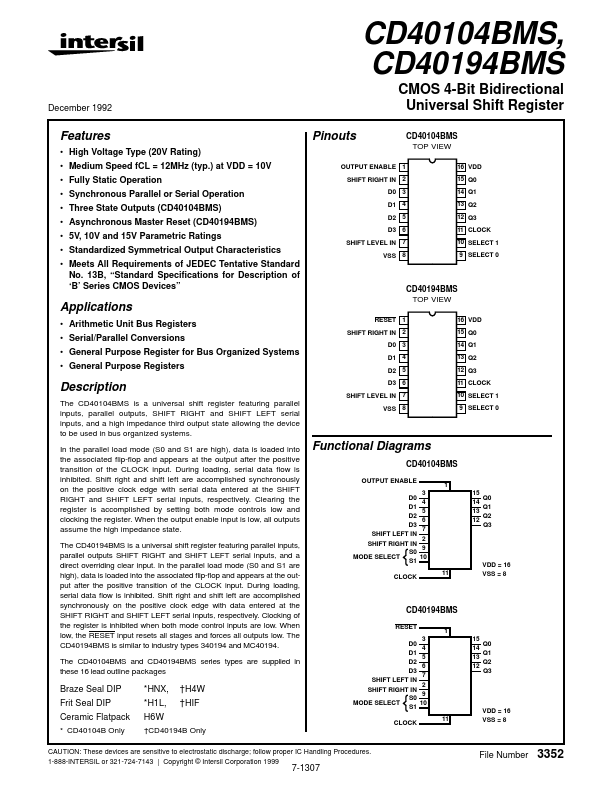

The CD40104BMS is a universal shift register featuring parallel inputs, parallel outputs, SHIFT RIGHT and SHIFT LEFT serial inputs, and a high impedance third output state allowing the device to be used in bus organized systems. In the parallel load mode (S0 and S1 are high), data is loaded into the associated flip-flop and appears at the output after the positive transition of the CLOCK input.

- High Voltage Type (20V Rating)

- Medium Speed fCL = 12MHz (typ.) at VDD = 10V

- Fully Static Operation

- Synchronous Parallel or Serial Operation

- Three State Outputs (CD40104BMS)

- Asynchronous Master Reset (CD40194BMS)

- 5V, 10V and 15V Parametric Ratings

- Standardized Symmetrical Output Characteristics

- Meets All Requirements of JEDEC Tentative Standard No. 13B, “Standard Specifications for Description of ‘B’ Series CMOS Devices”