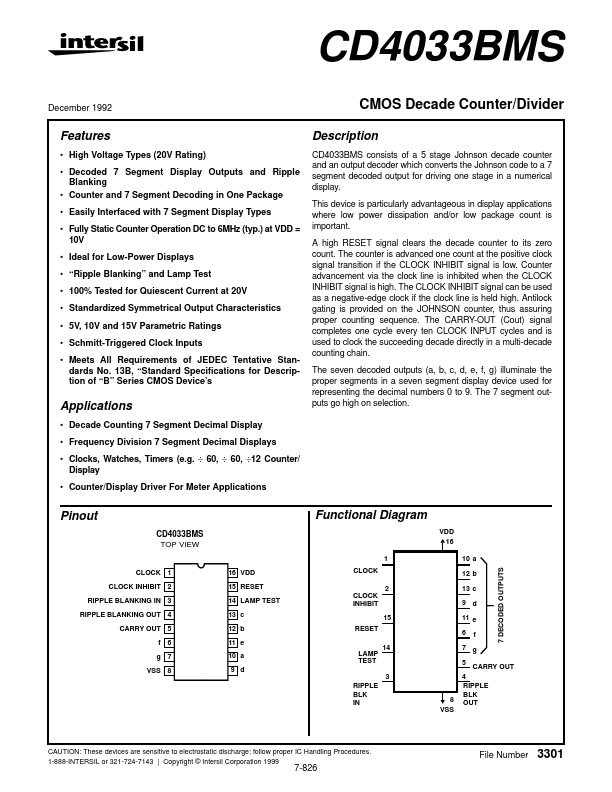

CD4033BMS Overview

CD4033BMS consists of a 5 stage Johnson decade counter and an output decoder which converts the Johnson code to a 7 segment decoded output for driving one stage in a numerical display. This device is particularly advantageous in display applications where low power dissipation and/or low package count is important. A high RESET signal clears the decade counter to its zero count.

CD4033BMS Key Features

- High Voltage Types (20V Rating)

- Decoded 7 Segment Display Outputs and Ripple Blanking

- Counter and 7 Segment Decoding in One Package

- Easily Interfaced with 7 Segment Display Types

- Fully Static Counter Operation DC to 6MHz (typ.) at VDD = 10V

- Ideal for Low-Power Displays

- 100% Tested for Quiescent Current at 20V

- Standardized Symmetrical Output Characteristics

- 5V, 10V and 15V Parametric Ratings