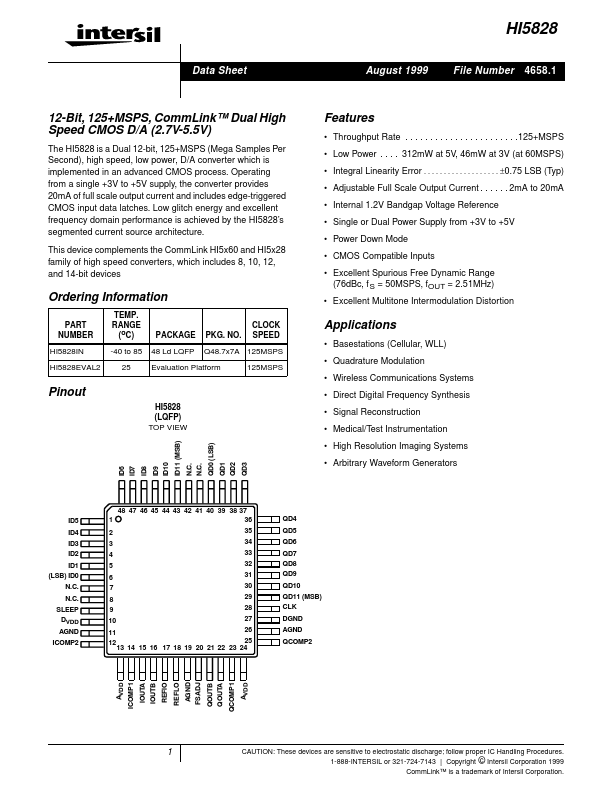

HI5828 Key Features

- Throughput Rate

- 125+MSPS

- Low Power . . . . 312mW at 5V, 46mW at 3V (at 60MSPS)

- Integral Linearity Error

- ±0.75 LSB (Typ)

- Adjustable Full Scale Output Current

- 2mA to 20mA

- Internal 1.2V Bandgap Voltage Reference

- Single or Dual Power Supply from +3V to +5V

- Power Down Mode