HM3-6514B-9

HM3-6514B-9 is 1024 x 4 CMOS RAM manufactured by Intersil.

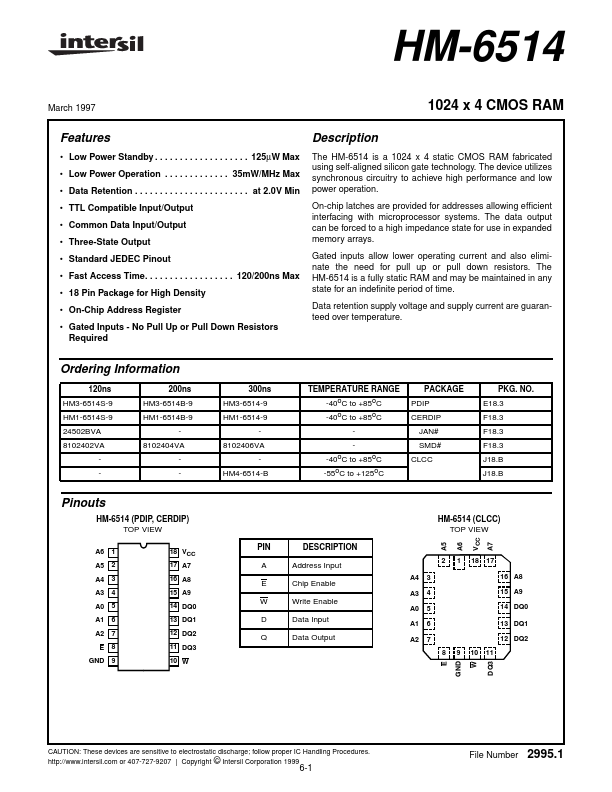

HM-6514

March 1997

1024 x 4 CMOS RAM

Description

The HM-6514 is a 1024 x 4 static CMOS RAM fabricated using self-aligned silicon gate technology. The device utilizes synchronous circuitry to achieve high performance and low power operation. On-chip latches are provided for addresses allowing efficient interfacing with microprocessor systems. The data output can be forced to a high impedance state for use in expanded memory arrays. Gated inputs allow lower operating current and also eliminate the need for pull up or pull down resistors. The HM-6514 is a fully static RAM and may be maintained in any state for an indefinite period of time. Data retention supply voltage and supply current are...