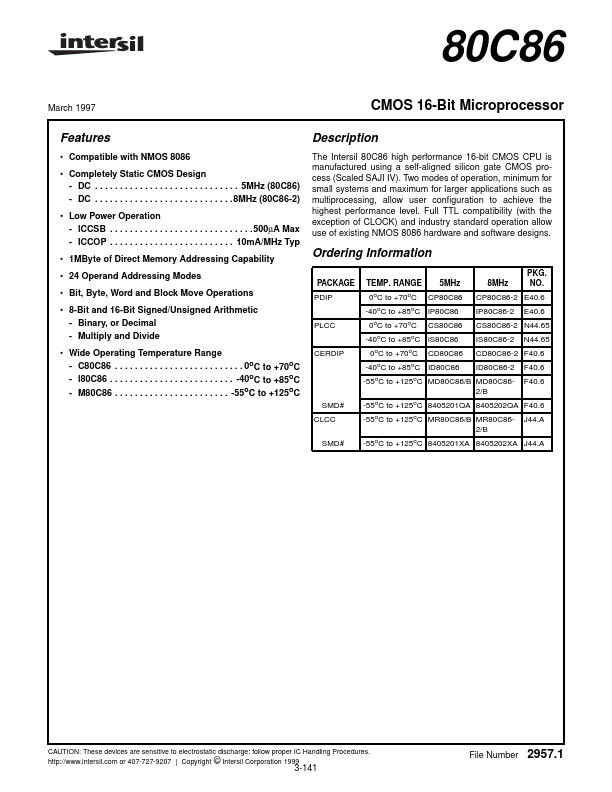

ID80C86

Description

The Intersil 80C86 high performance 16-bit CMOS CPU is manufactured using a self-aligned silicon gate CMOS process (Scaled SAJI IV). Two modes of operation, minimum for small systems and maximum for larger applications such as multiprocessing, allow user configuration to achieve the highest performance level.

Key Features

- compatible with NMOS 8086

- pletely Static CMOS Design

- DC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5MHz (80C86)

- DC . . . . . . . . . . . . . . . . . . . . . . . . . . . .8MHz (80C86-2)

- Low Power Operation

- lCCSB . . . . . . . . . . . . . . . . . . . . . . . . . . . . .500µA Max

- ICCOP . . . . . . . . . . . . . . . . . . . . . . . . . 10mA/MHz Typ

- 1MByte of Direct Memory Addressing Capability

- 24 Operand Addressing Modes

- 8-Bit and 16-Bit Signed/Unsigned Arithmetic