X4043

Overview

- Selectable watchdog timer

- Low VCC detection and reset assertion -Five standard reset threshold voltages -Adjust low VCC reset threshold voltage using special programming sequence -Reset signal valid to VCC = 1V

- Low power CMOS -<20µA max standby current, watchdog on -<1µA standby current, watchdog OFF -3mA active current

- 4kbits of EEPROM -16-byte page write mode -Self-timed write cycle -5ms write cycle time (typical)

- Built-in inadvertent write protection -Power-up/power-down protection circuitry -Protect 0, 1/4, 1/2, all or 16, 32, 64 or 128 bytes of EEPROM array with Block Lock™ protection

- 400kHz 2-wire interface

- 2.7V to 5.5V power supply operation

- Available packages -8 Ld SOIC -8 Ld MSOP -8 Ld PDIP

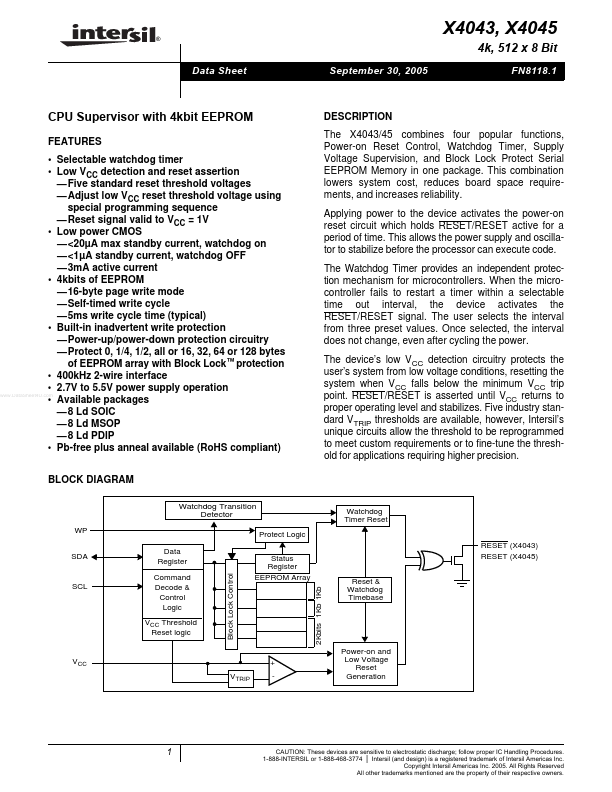

- Pb-free plus anneal available (RoHS compliant) BLOCK DIAGRAM Watchdog Transition Detector WP SDA Data Register Command Decode & Control Logic VCC Threshold Reset logic Block Lock Control Protect Logic Status Register EEPROM Array 2Kbits 1Kb 1Kb