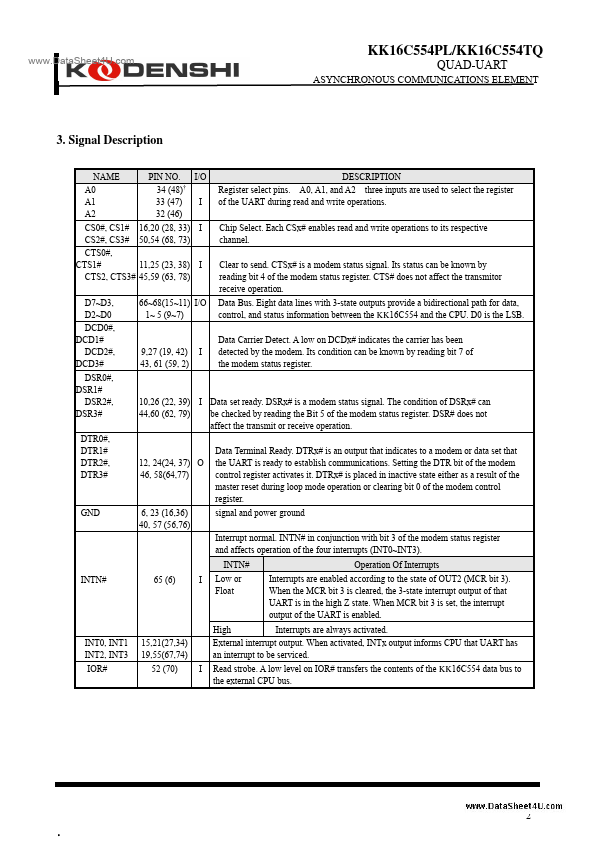

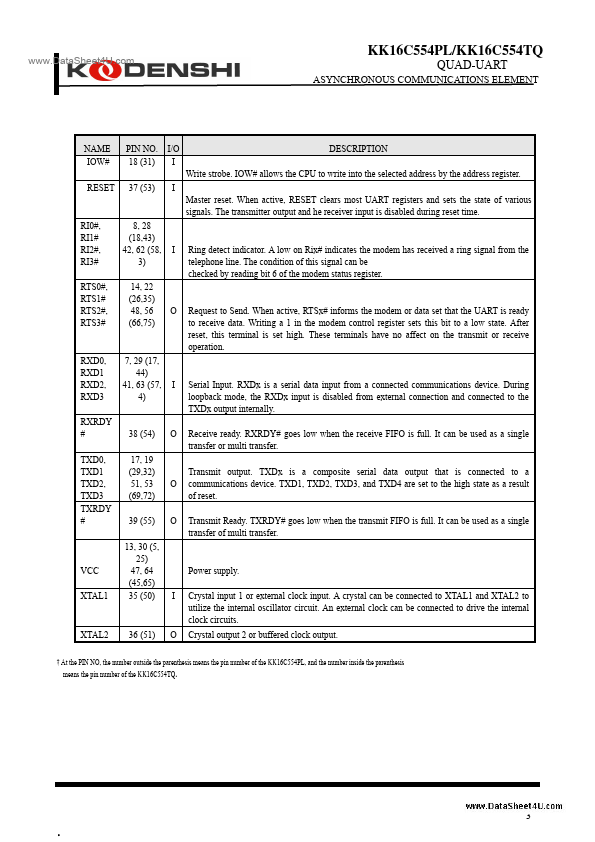

Datasheet Summary

..

KK16C554PL/KK16C554TQ

QUAD-UART

ASYNCHRONOUS MUNICATIONS ELEMENT

1. General Description

KK16C554 is an enhanced quadruple version of the 16C550 UART (Universal Asynchronous Receiver Transmitter). Each channel can be put into FIFO mode to relieve the CPU of excessive software overhead. In this mode, internal FIFOs are activated and 16 bytes plus 3 bit of error data per byte can be stored in both receive and transmit modes. Each channel performs serial-to-parallel conversion on data characters received from a peripheral device or a MODEM, and parallel-to-serial conversion on data characters received from the CPU. The CPU can read the plete status of the UART at...