ISPLSI1048EA

ISPLSI1048EA is In-System Programmable High Density PLD manufactured by Lattice Semiconductor.

Features

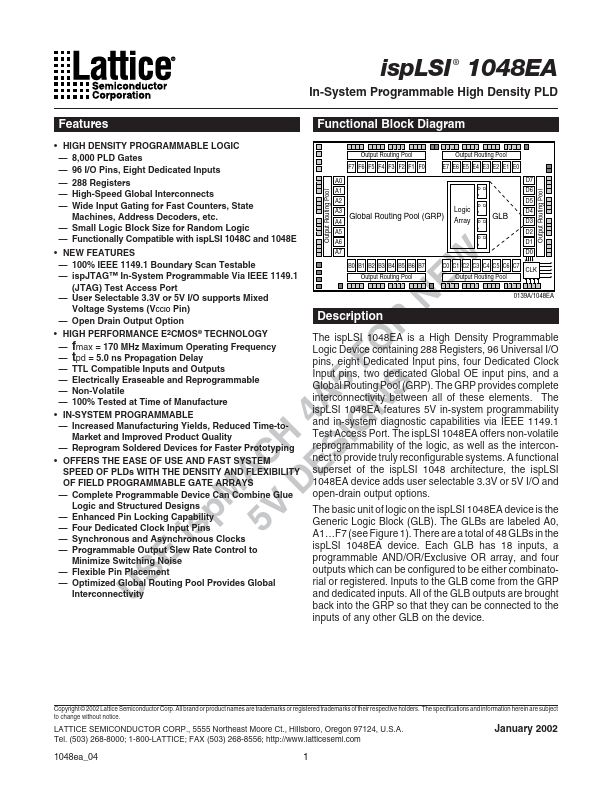

Functional Block Diagram

USE is5p VMDAECSIHG4NAS5 FOR

- HIGH DENSITY PROGRAMMABLE LOGIC

- 8,000 PLD Gates

- 96 I/O Pins, Eight Dedicated Inputs

- 288 Registers

- High-Speed Global Interconnects

- Wide Input Gating for Fast Counters, State Machines, Address Decoders, etc.

- Small Logic Block Size for Random Logic

- Functionally patible with isp LSI 1048C and 1048E

- NEW FEATURES

- 100% IEEE 1149.1 Boundary Scan Testable

- isp JTAG™ In-System Programmable Via IEEE 1149.1

(JTAG) Test Access Port

- User Selectable 3.3V or 5V I/O supports Mixed

Voltage Systems (VCCIO Pin)

- Open Drain Output Option

- HIGH PERFORMANCE E2CMOS® TECHNOLOGY

- fmax = 170 MHz Maximum Operating Frequency

- tpd = 5.0 ns Propagation Delay

- TTL patible Inputs and Outputs

- Electrically Eraseable and Reprogrammable

- Non-Volatile

- 100% Tested at Time of Manufacture

- IN-SYSTEM PROGRAMMABLE

-...