ISPLSI5512VE

Overview

- Second Generation SuperWIDE HIGH DENSITY IN-SYSTEM PROGRAMMABLE LOGIC DEVICE - 3.3V Power Supply - User Selectable 3.3V/2.5V I/O - 24000 PLD Gates / 512 Macrocells - Up to 256 I/O Pins - 512 Registers - High-Speed Global Interconnect - SuperWIDE Generic Logic Block (32 Macrocells) for Optimum Performance - SuperWIDE Input Gating (68 Inputs) for Fast Counters, State Machines, Address Decoders, etc. - PCB Efficient Ball Grid Array (BGA) Package Options - Interfaces with Standard 5V TTL Devices

- HIGH PERFORMANCE E2CMOS® TECHNOLOGY - fmax = 155 MHz Maximum Operating Frequency - tpd = 6.5 ns Propagation Delay - TTL/3.3V/2.5V Compatible Input Thresholds and Output Levels - Electrically Erasable and Reprogrammable - Non-Volatile - Programmable Speed/Power Logic Path Optimization

- IN-SYSTEM PROGRAMMABLE - Increased Manufacturing Yields, Reduced Time-toMarket, and Improved Product Quality - Reprogram Soldered Devices for Faster Debugging

- 100% IEEE 1149.1 BOUNDARY SCAN TESTABLE AND 3.3V IN-SYSTEM PROGRAMMABLE

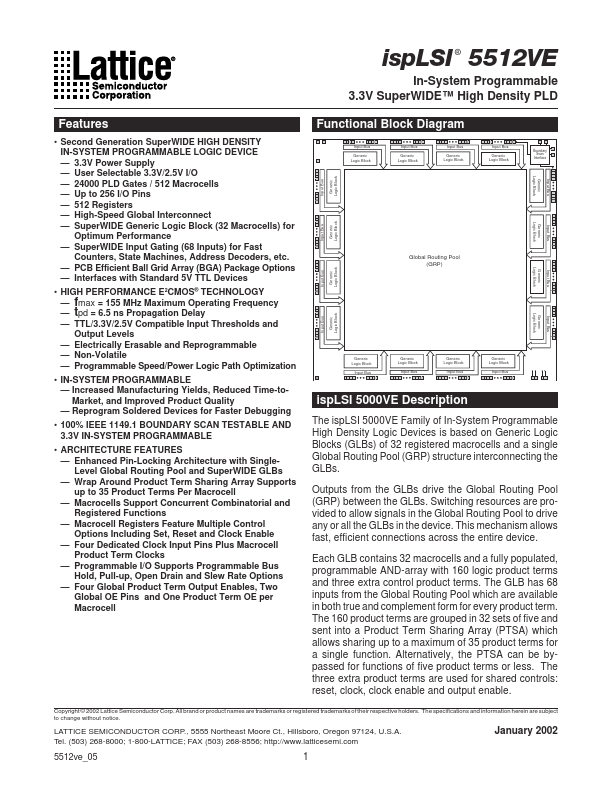

- ARCHITECTURE FEATURES - Enhanced Pin-Locking Architecture with SingleLevel Global Routing Pool and SuperWIDE GLBs - Wrap Around Product Term Sharing Array Supports up to 35 Product Terms Per Macrocell - Macrocells Support Concurrent Combinatorial and Registered Functions - Macrocell Registers Feature Multiple Control Options Including Set, Reset and Clock Enable - Four Dedicated Clock Input Pins Plus Macrocell Product Term Clocks - Programmable I/O Supports Programmable Bus Hold, Pull-up, Open Drain and Slew Rate Options - Four Global Product Term Output Enables, Two Global OE Pins and One Product Term OE per Macrocell Functional Block Diagram Input Bus Generic Logic Block Input Bus Generic Logic Block Input Bus Generic Logic Block Input Bus Generic Logic Block Boundary Scan Interface Input Bus Generic Logic Bloc