ORSPI4 Description

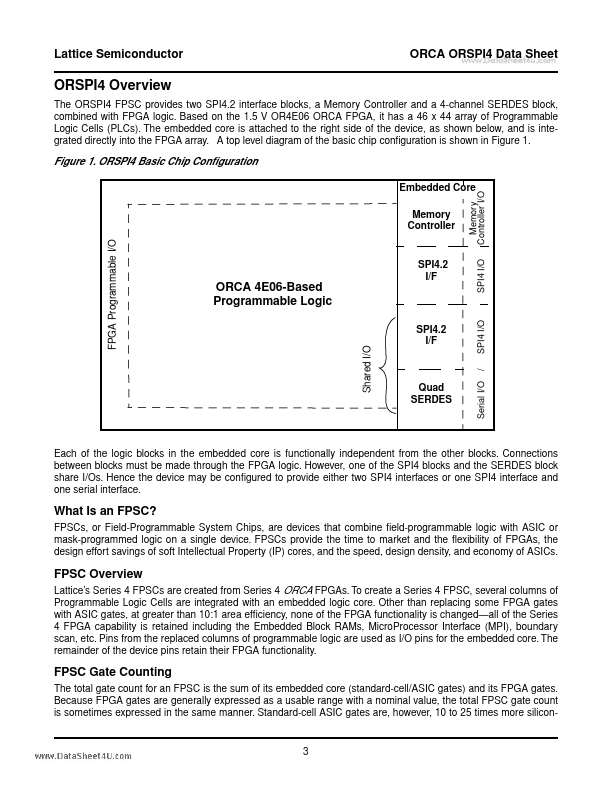

Dual SPI4 Interface and High-Speed SERDES FPSC October 2007 Data Sheet Lattice Semiconductor has developed a next-generation FPSC targeted at high-speed data transmission. Built on the Series 4 reconfigurable embedded System-on-a-Chip (SoC) architecture, the ORSPI4 FPSC contains two SPI4.2 interface blocks, a high-speed Memory Controller, four channels of 0.6-3.7 Gbits/s SERDES with 8b/10b encoding and decoding and...

ORSPI4 Key Features

- Full bandwidth up to 450 MHz DDR (900 Mbits/s) for all speed grades

- Bit de-skewing up to 16 phases of the clock

- Capable of aligning bit-to-bit skews as large as ±1 bit periods Static timing receive interface

- Speeds up to 325 MHz DDR (650 Mbits/s), for all speed grades, including Quarter-Rate mode

- Clock aligned or clock centered modes supported DIP-4 and DIP-2 parity generation and checking Transmit Interface

- Speeds up to 450 MHz DDR (900 Mbits/s)

- Dedicated LVDS transmit interface for improved data eye integrity

- Automatic idle insertion 256 logical ports

- Embedded Calendar-based sequence port polling mechanism and bandwidth allocation. Shadow Calendar support for smooth tra

- Up to 32 independent TX and 32 independent RX buffers per SPI4 interface internally. Various aggregation modes to suppor