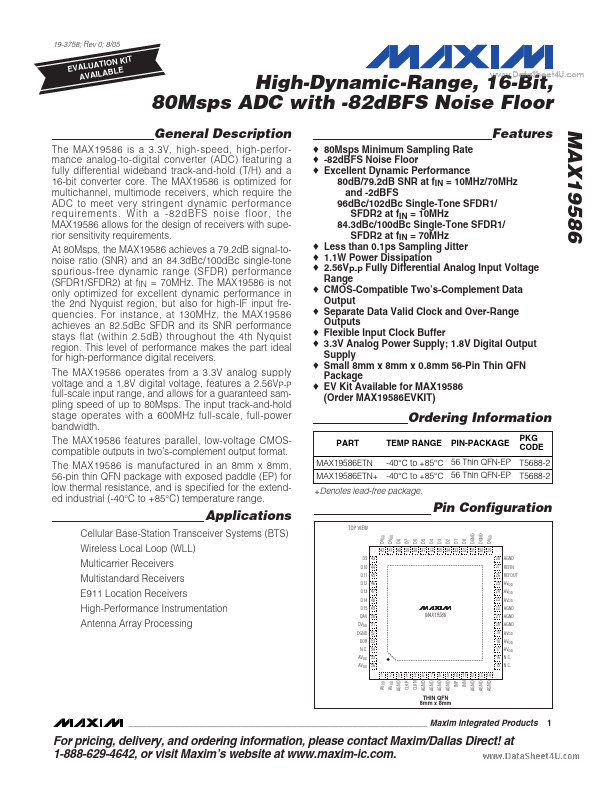

MAX19586 Description

1.8V Digital Output Supply o Small 8mm x 8mm x 0.8mm 56-Pin Thin QFN Package o EV Kit Available for MAX19586 (Order MAX19586EVKIT) .. MAX19586 The MAX19586 is a 3.3V, high-speed, high-performance analog-to-digital converter (ADC) featuring a fully differential wideband track-and-hold (T/H) and a 16-bit converter core. The MAX19586 is optimized for multichannel, multimode receivers, which require the ADC to meet very...