SY58608U Overview

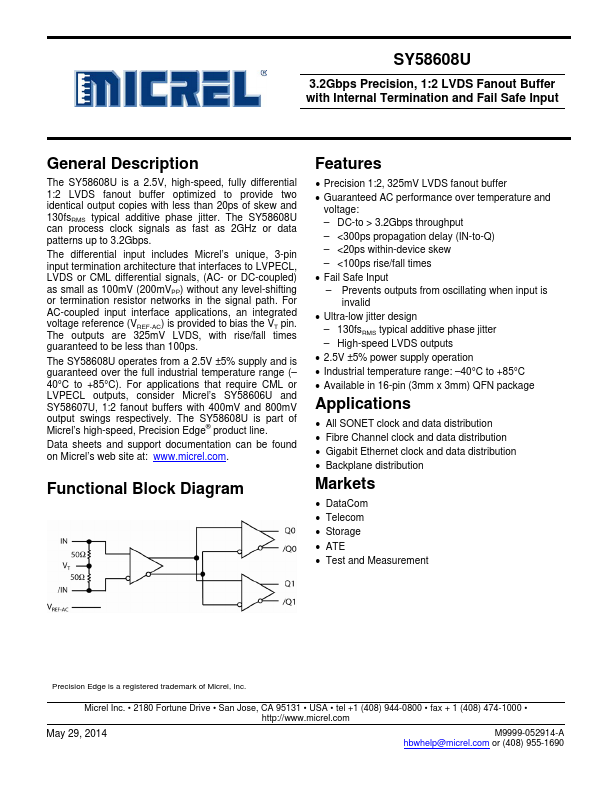

The SY58608U is a 2.5V, high-speed, fully differential 1:2 LVDS fanout buffer optimized to provide two identical output copies with less than 20ps of skew and 130fsRMS typical additive phase jitter. The SY58608U can process clock signals as fast as 2GHz or data patterns up to 3.2Gbps. The differential input includes Micrel’s unique, 3-pin input termination architecture that interfaces to LVPECL, LVDS or CML...

SY58608U Key Features

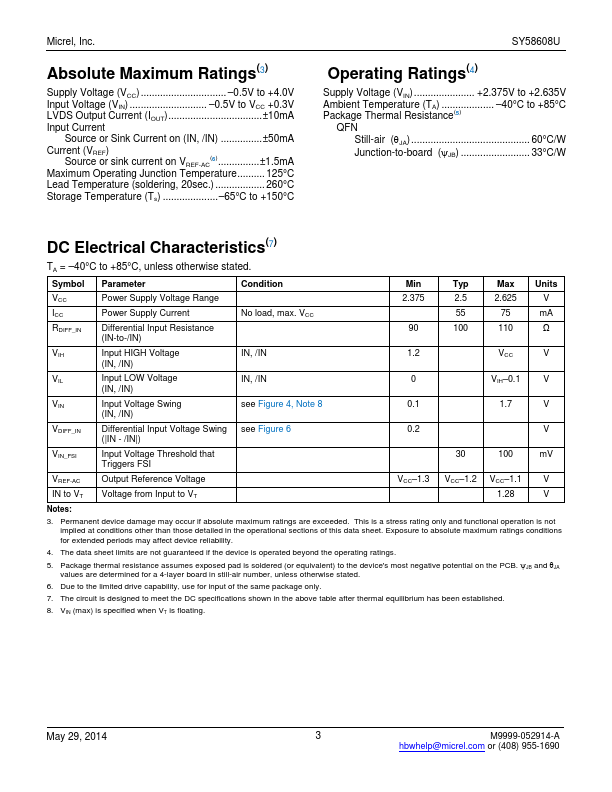

- Precision 1:2, 325mV LVDS fanout buffer

- Guaranteed AC performance over temperature and

- DC-to > 3.2Gbps throughput

- <300ps propagation delay (IN-to-Q)

- <20ps within-device skew

- <100ps rise/fall times

- Fail Safe Input

- Prevents outputs from oscillating when input is

- Ultra-low jitter design

- 130fsRMS typical additive phase jitter