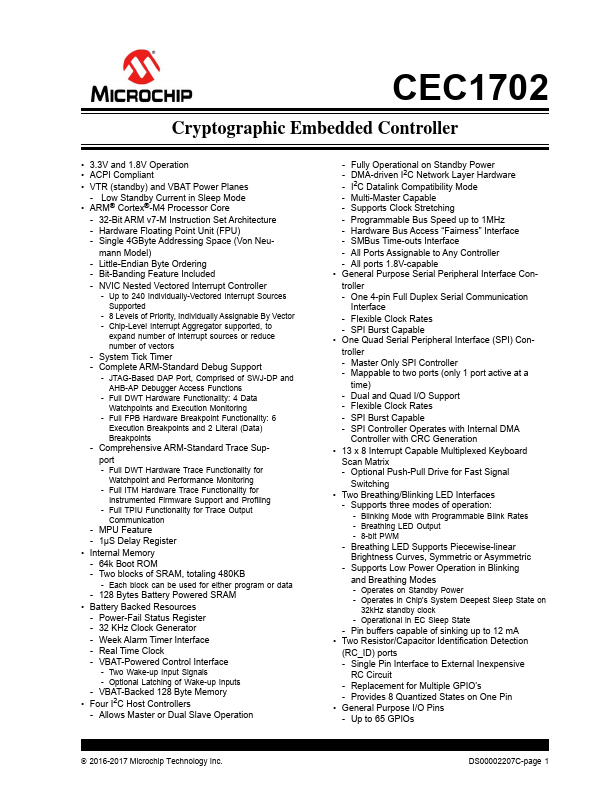

CEC1702 Overview

Key Specifications

Pins: 84

Key Features

- NVIC Nested Vectored Interrupt Controller

- Up to 240 Individually-Vectored Interrupt Sources Supported

- 8 Levels of Priority, Individually Assignable By Vector

- Chip-Level Interrupt Aggregator supported, to expand number of interrupt sources or reduce number of vectors

- System Tick Timer