DSPIC30F2020

DSPIC30F2020 is SMPS 16-Bit Digital Signal Controller manufactured by Microchip Technology.

- Part of the DSPIC30F1010 comparator family.

- Part of the DSPIC30F1010 comparator family.

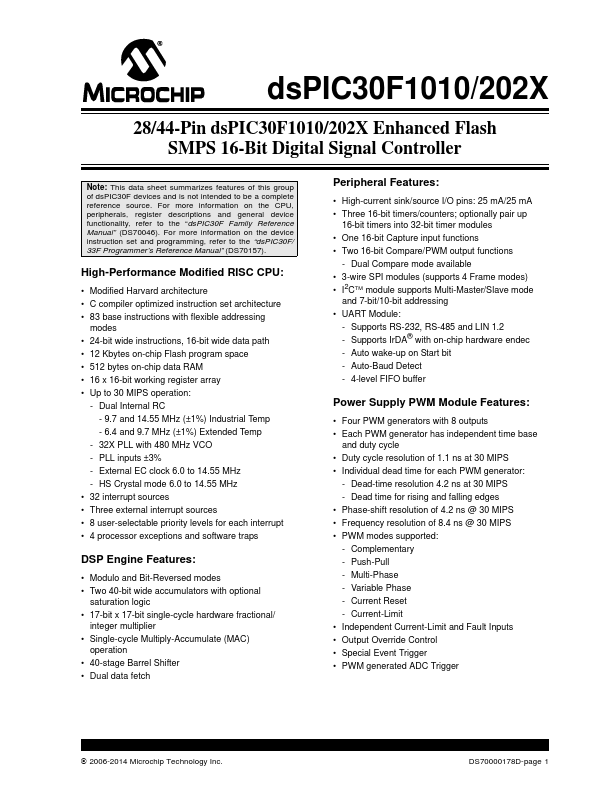

dsPIC30F1010/202X

28/44-Pin dsPIC30F1010/202X Enhanced Flash SMPS 16-Bit Digital Signal Controller

Note: This data sheet summarizes Features of this group of dsPIC30F devices and is not intended to be a plete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the “dsPIC30F Family Reference Manual” (DS70046). For more information on the device instruction set and programming, refer to the “dsPIC30F/ 33F Programmer’s Reference Manual” (DS70157).

High-Performance Modified RISC CPU:

- Modified Harvard architecture

- C piler optimized instruction set architecture

- 83 base instructions with flexible addressing...