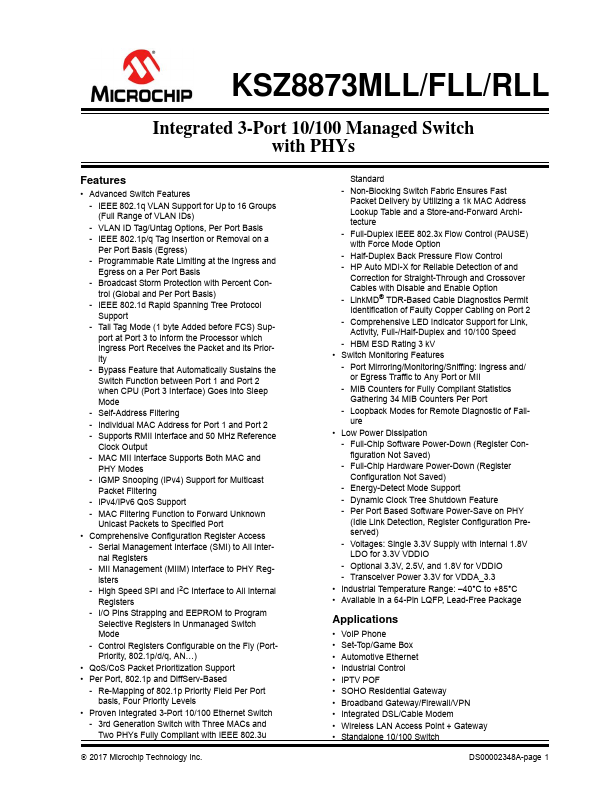

KSZ8873MLL

Overview

- Advanced Switch Features - IEEE 802.1q VLAN Support for Up to 16 Groups (Full Range of VLAN IDs) - VLAN ID Tag/Untag Options, Per Port Basis - IEEE 802.1p/q Tag Insertion or Removal on a Per Port Basis (Egress) - Programmable Rate Limiting at the Ingress and Egress on a Per Port Basis - Broadcast Storm Protection with Percent Control (Global and Per Port Basis) - IEEE 802.1d Rapid Spanning Tree Protocol Support - Tail Tag Mode (1 byte Added before FCS) Support at Port 3 to Inform the Processor which Ingress Port Receives the Packet and its Priority - Bypass Feature that Automatically Sustains the Switch Function between Port 1 and Port 2 when CPU (Port 3 Interface) Goes into Sleep Mode - Self-Address Filtering - Individual MAC Address for Port 1 and Port 2 - Supports RMII Interface and 50 MHz Reference Clock Output - MAC MII Interface Supports Both MAC and PHY Modes - IGMP Snooping (IPv4) Support for Multicast Packet Filtering - IPv4/IPv6 QoS Support - MAC Filtering Function to Forward Unknown Unicast Packets to Specified Port

- Comprehensive Configuration Register Access - Serial Management Interface (SMI) to All Internal Registers - MII Management (MIIM) Interface to PHY Registers - High Speed SPI and I2C Interface to All Internal Registers - I/O Pins Strapping and EEPROM to Program Selective Registers in Unmanaged Switch Mode - Control Registers Configurable on the Fly (PortPriority, 802.1p/d/q, AN…)

- QoS/CoS Packet Prioritization Support

- Per Port, 802.1p and DiffServ-Based - Re-Mapping of 802.1p Priority Field Per Port basis, Four Priority Levels

- Proven Integrated 3-Port 10/100 Ethernet Switch - 3rd Generation Switch with Three MACs and Two PHYs Fully Compliant with IEEE 802.3u 2017 Microchip Technology Inc. Standard - Non-Blocking Switch Fabric Ensures Fast Packet Delivery by Utilizing a 1k MAC Address Lookup Table and a Store-and-Forward Architecture - Full-