PIC18F56Q43

Description

The PIC18-Q43 microcontroller family is available in 28/40/44/48-pin devices for real-time control applications. This family features a 12-bit Analog-to-Digital Converter with Computation (ADCC) automating Capacitive Voltage Divider (CVD) techniques for advanced capacitive touch sensing, averaging, filtering, oversampling and threshold comparison.

Key Features

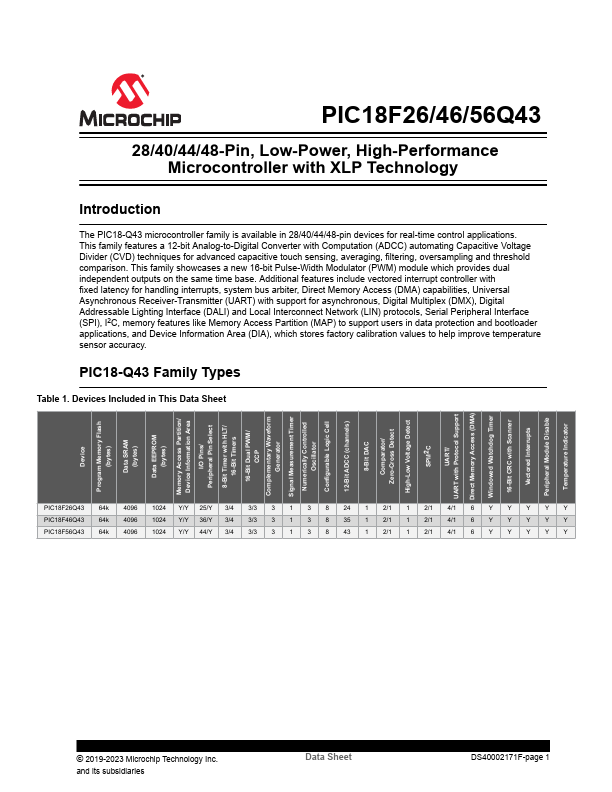

- Devices Included in This Data Sheet